## SOI Photonic Crystal Fabrication Using Deep UV Lithography

Wim Bogaerts\*, Dirk Taillaert\*, Roel Baets\*, Vincent Wiaux\*\*, Stephan Beckx\*\*, Mireille Maenhoudt\*\*, Geert Vandenberghe\*\*.

- \* Ghent University-IMEC, Dept. of Information Technology Sint-Pietersnieuwstraat 41, 9000 Gent, Belgium

- \*\* IMEC vzw, Silicon Process Technology Division Kapeldreef 75, B-3001 Leuven, Belgium

We present first result of photonic crystal-like structures in Silicon-on-Insulator (SOI) fabricated with deep UV lithography.

Photonic crystals provide an elegant way to the design of ultra-compact photonic integrated circuits (PICs). One major limitation for the widespread use of these structures is the lack of efficient fabrication technologies. Most photonic crystals today are defined using e-beam lithography, a technique which can handle the resolutions required for photonic crystals at telecom wavelengths, but lacks the possibility for industrial application due to long writing times. Other techniques used for the large-scale fabrication of current PICs cannot print the fine details of photonic crystals.

Deep UV lithography has the promise to solve this issue. This optical lithography technique based on excimer lasers with wavelength of 248nm and shorter is being implemented in the current state-ofthe-art CMOS-facilities. These short wavelengths (Currently 248nm, with 193nm-technology in development and research being conducted on 157nm) can resolve periodic structures with periods down to a few 100nm.

Our material of choice is Silicon-on-Insulator. SOI is a good material system for the fabrication of Photonic Crystals because it is transparent for the main telecom wavelenghts, it has a high refractive index contrast and it can be processed in silicon-based facilities.

As photonic crystal structures differ significantly from typical CMOS-circuits, lithography knowledge cannot be ported in a straightforward manner to photonic crystals. Key differences between these two types of structures are the lattice type (preferably triangular for photonic crystals versus square in CMOS-circuits) and the fill factor of the unit cell. In contrast with common photonic crystal structures, CMOS technologies do not use holes where the hole diameter is larger than the spacing in between holes. We have therefore studied the possibilities of manufacturing photonic crystal-like structures with this technology. For this purpose we used the 248nm deep UV lithography facilities available at IMEC. These consist of an ASML PAS 5500/300 DUV stepper attached to an automated wafer processing track.

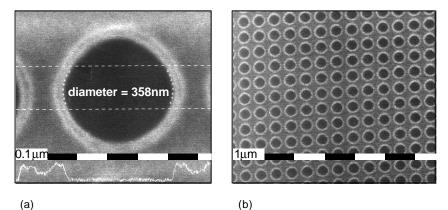

Figure 1: Resist patters of superdensely packed holes fabricated using overexposure. Lattice constant is 500nm, hole diameter targeted at 350nm.

First lithography and etch tests show promising results. For these tests we used a CMOS mask with square lattices of holes with a fill factor r/a of 0.25 (dense holes, where the hole diameter is equal to the hole spacing) or less (semi-dense or isolated holes). To fabricate lattices with higher fill factors

(superdense holes) using the same mask, we applied overexposure, illuminating the photo-resist with a higher energy dose. This technique proves that with deep UV lithography lattices of superdense holes can be made. For our lithography tests we fabricated dense lattices with 250nm hole/500nm pitch and 300nm hole/600nm pitch, and superdense lattices of 300nm hole/560nm pitch and 300nm hole/520nm pitch using lithographic overexposure. For all these targets the process had an adequate budget in lithography parameters like focus and exposure dose.

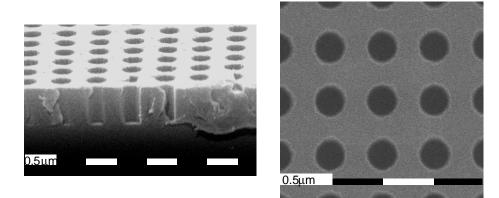

The etching process of these structures are evaluated on Silicon substrates on which 400nm  $\text{SiO}_2$  and 200nm amorphous silicon were deposited. This structure differs optically from crystalline SOI, but has similar etch properties and a substantially lower cost per wafer. Etch tests show holes with straight sidewalls in both the a-Si layer and the oxide layer, with no discernable discontinuities between the different layers. Sidewalls have little deviation from the vertical and show very little roughness (Figure 2).

Figure 2: 250nm densely packed holes (r/a=0.25) in SOI. The a-Si top layer is 200nm thick, the oxide 400nm.

One of the major drawbacks of optical lithography with densely packed structures is the occurrence of optical proximity effects. When these structures are illuminated, the pattern of each hole interferes slightly with that of neighbouring holes, thereby modifying the hole size. The latter could therefore show a dependency to the density of the lattice. Therefore, defect structures in photonic crystals (e.g. channel waveguides or cavities), where holes lacks neighbours in certain directions, might print differently than holes fully surrounded in the lattice. The same is true for corners and cavities. Therefore *optical proximity corrections* (OPC) should be included on the mask to compensate for this effect. We have designed a mask to determine the necessary OPCs for photonic crystal structures with a triangular lattice. This mask contains an imaginary photonic integrated circuit with waveguides and cavities of various sizes and geometries to evaluate the correct parameters for fabricating a wide range of photonic crystal structures.

Preliminary studies show that deep UV lithography is a good candidate for the mass-manufacturing of photonic crystal-based PICs. First lithography and etch tests on photonic crystal-like structure show promising results.

- This work is supported by the European Union in the context of the IST project PICCO.

- Wim Bogaerts acknowledges the Flemish Institute for the industrial advancement of Scientific and Technological Research (IWT) for a specialisation grant.

Peter Bienstman acknowledges the Flemish National Fund for Scientific Research (FWO-Vlaanderen) for a doctoral fellowship.