# Integration of III-V light sources on a silicon photonics circuit by transfer printing

Joan Juvert, Tommaso Cassese, Sarah Uvin, Andreas De Groote, Brad Snyder, Peter De Heyn, Peter Verheyen, António José Trindade, Christopher Bower, Marco Romagnoli, Günther Roelkens, and Dries Van Thourhout

Abstract—We report on the integration by transfer printing of III-V Fabry-Pérot cavities on a silicon photonic circuit. We pre-process the III-V coupons on their native substrate, transfer print onto the target SOI, and post-process the printed coupons. We report light coupling into the photonic circuit.

Index Terms—laser integration, transfer printing, Si photonics integrated circuits

### I. Introduction

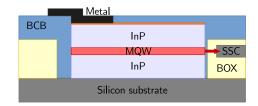

► UE to the lack of a viable silicon light source for silicon photonics, heterogeneous integration of III-V sources on SOI photonic circuits has received a lot of attention. In this work we use transfer printing [1] to integrate pre-processed III-V coupons onto a standard silicon photonics integrated circuit. Transfer printing allows an optimal use of the source III-V material and parallel operation for massive integration. In order to leverage the enhanced heat dissipation of silicon, our approach is to print the III-V coupons in trenches etched in the buried oxide (BOX) in such a way that the III-V rests on the silicon substrate. The thickness of the bottom cladding in the III-V epitaxial stack is adjusted so that the multi quantum wells (MQW) are level with the silicon on the target photonic circuit, as shown in Fig. 1. The output of the MQW device is then directly coupled to the silicon waveguide in the SOI by means of a trident spot-size converter [2].

# II. PRE-PROCESSING

The III-V coupons are pre-processed on a commercial III-V epi stack supplied by Smart Photonics. The MQW stack consists of 4 pairs of 6 nm InGaAsP QW and  $12\,\mathrm{nm}$  barriers and has a photoluminescence peak at  $1550\,\mathrm{nm}$ , sandwiched between  $50\,\mathrm{nm}$  thick, Q1.25 separate confinement heterostructure (SCH) layers. The top cladding is  $1.5\,\mu\mathrm{m}$  of p-doped InP whereas the bottom cladding is a  $2.4\,\mu\mathrm{m}$  thick n-doped InP

This work was supported by the EU through the H2020 project Teraboard (688510) funded in the context of Photonics PPP, the TOPHIT project and by imee's industry-affiliation program on Optical I/O.

Joan Juvert, Sarah Uvin, Andreas De Groote, Günther Roelkens and Dries Van Thourhout are with the Photonics Research Group, INTEC-department, Ghent University-IMEC and the Center for Nano- and Biophotonics (NB-Photonics), Ghent University, Belgium.

Tommaso Cassese is with the Scuola Superiore Sant'Anna - TeCIP Institute, Pisa, Italy.

Marco Romagnoli is with the Consorzio Nazionale Interuniversitario per le Telecomunicazioni (CNIT), Pisa, Italy

Brad Snyder, Peter de Heyn and Peter Verheyen are with imec, Leuven,

António José Trindade and Christopher Bower are with X-Celeprint Limited, Cork, Ireland.

Fig. 1. Sketch of the integration approach. The III-V coupon is transfer printed directly in a trench in the buried oxide. No adhesive layer is used for the bonding. The output of the MQW device is directly coupled to a trident spot-size converter, SSC in the picture, in the photonic circuit. The whole structure is passivated with BCB after transfer printing.

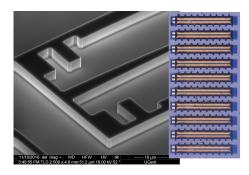

Fig. 2. SEM image of the front side of the main mesa. The trenches inside the mesa define the central waveguide. The notches in the trenches are used for pattern recognition during transfer printing. On the right, an optical image of an array of encapsulated coupons on their native III-V substrate is shown.

layer. Below the n cladding, a  $500\,\mathrm{nm}$  thick sacrificial InGaAs layer allows the release of the coupons. The top p contact consists of a  $200\,\mathrm{nm}$  thick InGaAs layer.

The main mesa of the coupons (50 µm wide and 400, 700 and 795 µm long) and the waveguides are defined by dry etching the III-V stack with Inductively Coupled Plasma Reactive Ion Etching (ICP-RIE) in two steps with a Plasma Enhanced Chemical Vapour Deposition (PECVD) silicon nitride hard mask. During the first step, the dry etch reaches around 500 nm below the MQW. After depositing a second PECVD nitride hard mask to protect the inner trenches and the laterally exposed MQW, the second step etches the main mesa further down to the interface between the n cladding and the release layer. As seen in Fig. 2, the dry etched walls are quite vertical and smooth.

After removing the nitride from the bottom of the inner trenches, the n metal contacts are deposited by evaporation. Next, a Piranha wet etch is used to vertically etch the InGaAs sacrificial layer around the coupon, creating a pedestal on

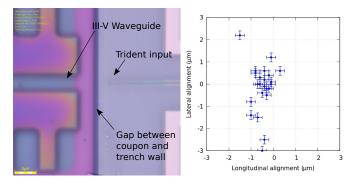

Fig. 3. Alignment accuracy. In the longitudinal direction (x axis), 0 would be perfect contact between the coupon and the trench wall.

top of which the coupon rests. Finally, the coupons are encapsulated with photoresist and the sacrificial layer is wet etched from under the coupons in a solution of FeCl<sub>3</sub>:H<sub>2</sub>O (1 g:2 ml) at 5 °C during  $110 \min [3]$ .

### III. TRANSFER-PRINTING

The coupons are transfer printed onto a SOI photonic circuit fabricated at IMEC and composed of a trident spot-size converter to couple the output of the III-V waveguide into the photonic circuit. Light is extracted from the system via a grating coupler. Before we can transfer print, we need to etch trenches in the buried oxide of the photonic circuit. We etch the BOX with an ICP-RIE dry etch without reaching the silicon substrate, and finish off with a Buffered Oxide Etch (BOE). The dry etch results in vertical trench walls, which is important since the coupons have to be transfer printed as close as possible to the spot-size converter. The final BOE results in a clean and smooth silicon surface without overetch, which is of paramount importance to achieve a strong enough Van Der Waals bonding between the coupon and the silicon without using any adhesive layer.

Once the trenches have been etched, the coupons are transfer printed from their native III-V substrate into the trenches. After the coupons have been printed, the photoresist is removed by RIE. The coupons are automatically aligned using pattern recognition software during transfer printing. The alignment accuracy thus obtained is within one micron, both laterally and longitudinally. Fig. 3 (left) shows in detail the front side of a transfer printed coupon and the measured alignment accuracy. Occasionally a coupon will not bond properly and move during peeling off of the stamp, which explains why we have a few outliers in Fig. 3. However, most coupons are clustered together within  $1\,\mu\mathrm{m}$  of the ideal position.

# IV. POST-PROCESSING

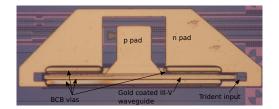

Once the coupons are printed on the target photonic circuit, the whole chip is passivated with DVS-BCB. RIE is used to open vias in the BCB along the longitudinal direction of the III-V waveguides before sputtering of the p metal contact along the waveguide. A second set of longitudinal vias in the BCB allows access to the n contacts that were deposited on the inner trenches of the coupons during pre-processing.

Fig. 4. Finished device. The central pad connects to the p contact along the coupon waveguide, whereas the lateral pads connect to the lateral n contacts on each inner trench.

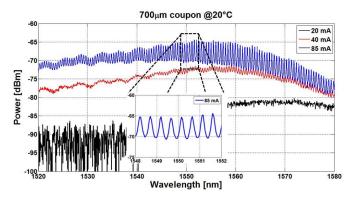

Fig. 5. Spectrum measured at different currents. The inset shows a free spectral range of  $500\,\mathrm{pm}$ , which is compatible with the  $700\,\mu\mathrm{m}$  long Fabry-Pérot cavity.

Finally the metal stack for the contact pads is deposited by sputtering/evaporation. Fig. 4 shows a finished device.

# V. CHARACTERIZATION

In order to check for successful coupling to the photonic circuit, we forward bias the devices and measure the light output from the grating coupler with an optical fiber connected to a spectrum analyzer. The results are shown in Fig. 5 for different current at  $20\,^{\circ}\mathrm{C}$ .

The total output power is  $250\,\mathrm{nW}$  at  $90\,\mathrm{mA}$  at  $5\,^\circ\mathrm{C}$ , or  $150\,\mathrm{nW}$  at the same current at  $20\,^\circ\mathrm{C}$ . It is worth noting that this includes the losses incurred due to the butt coupling from the coupon to the trident, in the trident itself, and in the grating coupler. The first is difficult to measure, but simulations indicate that we can expect losses around  $4\,\mathrm{dB}$  if the alignment is good in all three directions. Regarding the trident, simulations indicate losses of  $1.1\,\mathrm{dB}$ . Finally, using test structures we measure the losses in the grating coupler to be  $5.1\,\mathrm{dB}$ . Therefore, we can expect losses of at least around  $10\,\mathrm{dB}$  between the coupon and the fiber.

# REFERENCES

- [1] J. Justice, C. Bower, M. Meitl, M. B. Mooney, M. a. Gubbins, and B. Corbett, "Wafer-scale integration of group III–V lasers on silicon using transfer printing of epitaxial layers," *Nature Photonics*, vol. 6, no. 9, pp. 612–616, 2012.

- [2] N. Hatori, T. Shimizu, M. Okano, M. Ishizaka, T. Yamamoto, Y. Urino, M. Mori, T. Nakamura, and Y. Arakawa, "A hybrid integrated light source on a silicon platform using a trident spot-size converter," *Journal of Lightwave Technology*, vol. 32, no. 7, pp. 1329–1336, 2014.

- [3] A. De Groote, P. Cardile, A. Z. Subramanian, A. M. Fecioru, C. Bower, D. Delbeke, R. Baets, and G. Roelkens, "Transfer-printing-based integration of single-mode waveguide-coupled III-V-on-silicon broadband light emitters," *Optics Express*, vol. 24, no. 13, pp. 13754–13762, 2016.