# INTRODUCTION TO SILICON PHOTONICS CIRCUIT DESIGN

Wim Bogaerts

Short Course 454 - OFC 2018

### WHAT IS <u>SILICON</u> PHOTONICS?

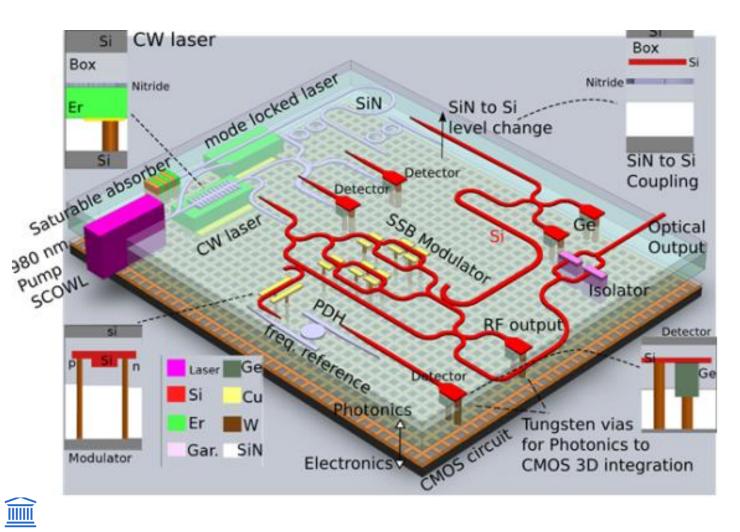

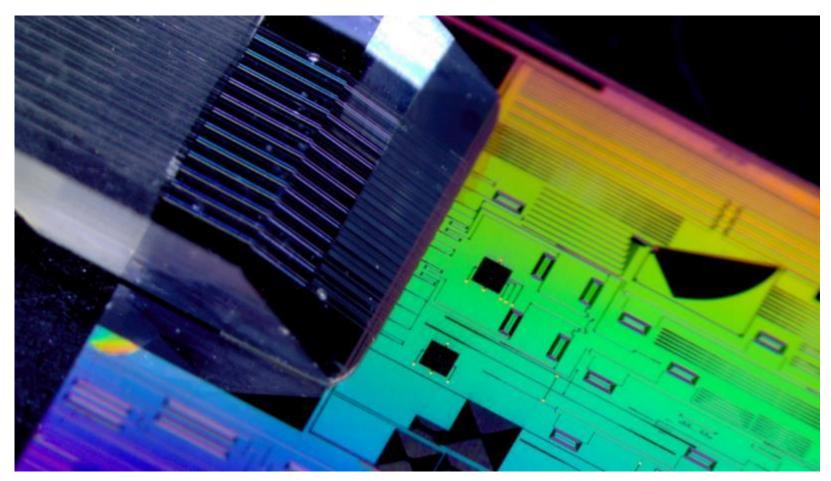

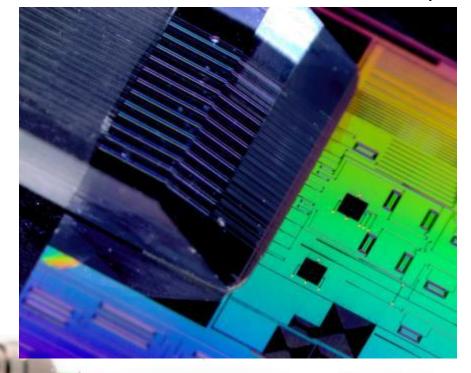

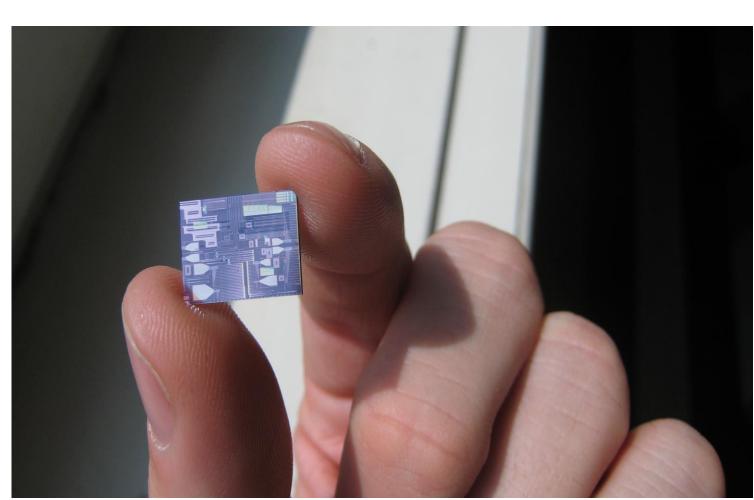

The implementation of <u>high density</u> photonic integrated circuits by means of CMOS process technology in a CMOS fab

Enabling complex optical functionality on a compact chip at low cost

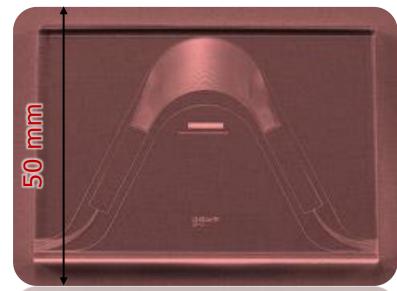

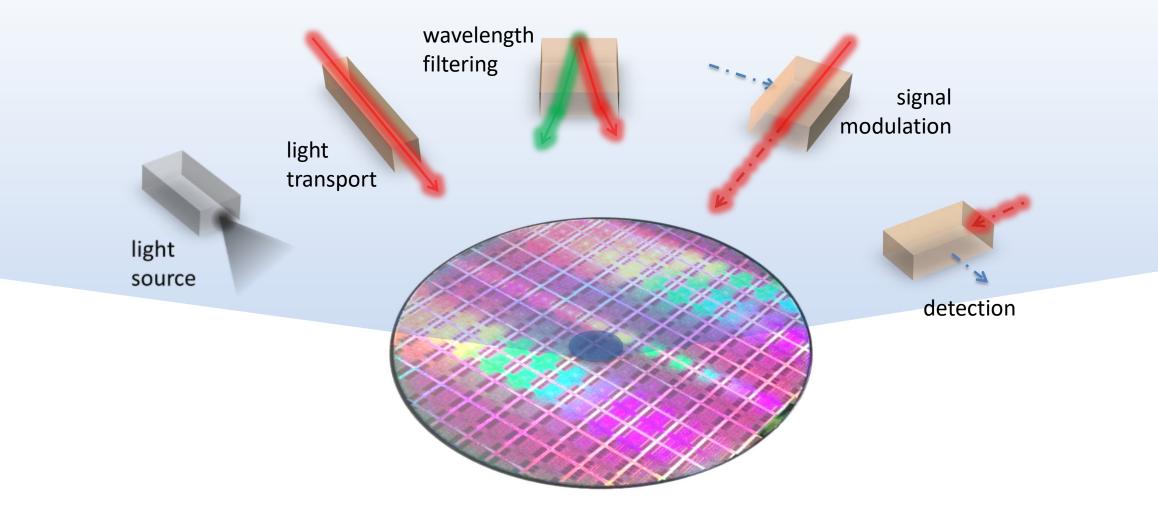

# PHOTONIC INTEGRATED CIRCUITS (PIC)

### Integration of (many) optical functions on a chip

GHENT

UNIVERSITY

unec

### INDUSTRIAL TAKE-UP EXAMPLES IN TELECOM/DATACOM/DATA CENTERS

- active optical cables (eg PSM4: 4x28 Gb/s on parallel fibers)

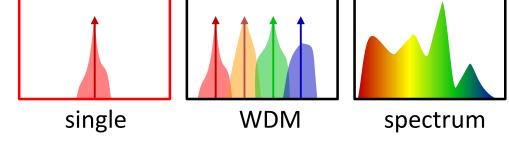

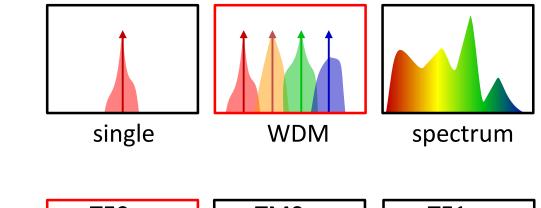

- WDM transceivers (eg 4 WDM channels x 25 Gb/s on single fiber)

- coherent receiver (eg 100 Gb/s PM-QPSK)

- fiber-to-the-home bidirectional transceiver (eg 12 x 2.5 Gb/s)

- monolithic receiver (eg 16x20Gb/s)

- 40Gb/s, 50Gb/s and 100 Gb/s Ethernet (future: 400Gb/s)

### WHY SILICON PHOTONICS?

# Large scale manufacturing

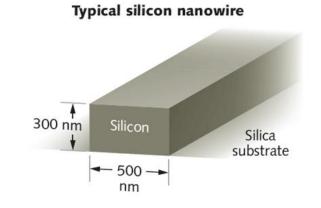

Submicron-scale waveguides

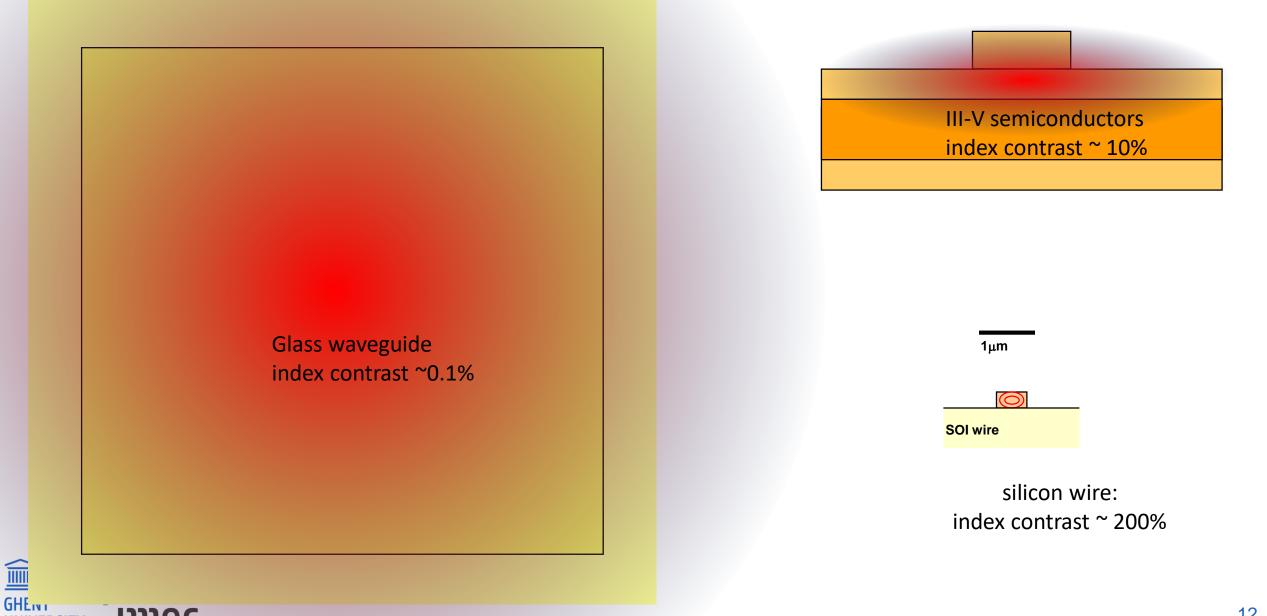

### SCALING OPTICAL WAVEGUIDES: INDEX CONTRAST

umec

UNIVERSITY

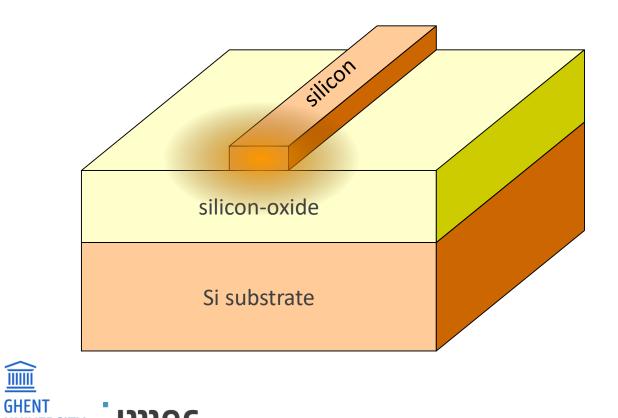

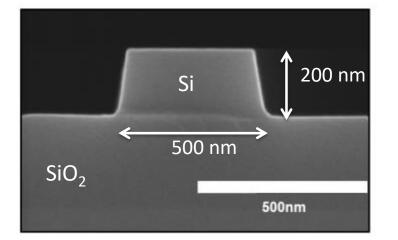

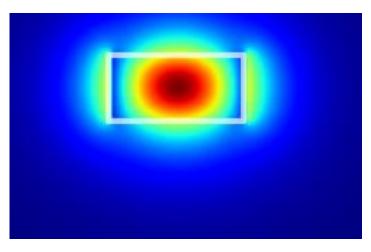

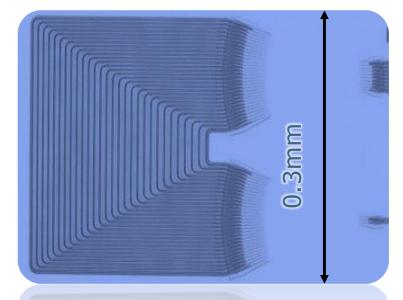

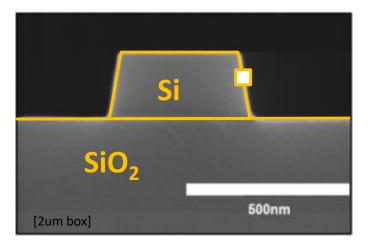

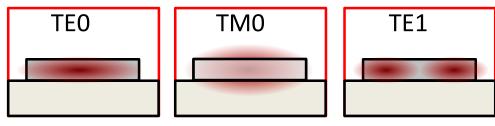

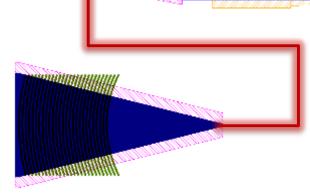

# WAVEGUIDES: SILICON PHOTONIC WIRES

### High contrast waveguides

unec

UNIVERSITY

- submicrometer dimensions

- small bend radius

optical mode

13

### HIGH INDEX CONTRAST: A BLESSING AND A CURSE

Very tight confinement of light

Very small bend radii : down to 1  $\mu m$

Very dense integration of components on a chip

Sub-wavelength design freedom

. .

nec

UNIVERSI

Photonic crystals with extremely high quality cavities

Cheben, OE, 2015

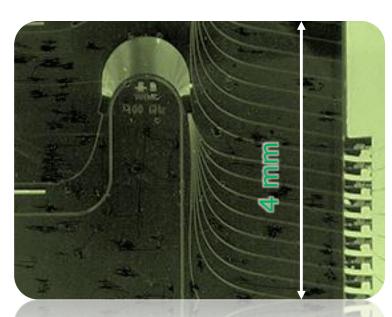

### HIGHER CONTRAST, SMALLER CORES, TIGHTER BENDS

#### Silica on silicon

Contrast ~ 0.01 - 0.1Mode diameter ~  $8\mu$ m Bend radius ~ 5mm Size ~  $10 \text{ cm}^2$

# 10000 ×

#### Indium Phosphide

Contrast ~ 0.2 - 0.5Mode diameter ~  $2\mu$ m Bend radius ~ 0.5mm Size ~ 10mm<sup>2</sup>

#### Silicon on insulator

Contrast ~ 1.0 - 2.5Mode diameter ~  $0.4\mu$ m Bend radius ~  $5\mu$ m Size ~ 0.1mm<sup>2</sup>

### HIGH INDEX CONTRAST: A BLESSING AND A CURSE

Every nm<sup>3</sup> matters

CMOS technology is the only manufacturing technology with sufficient nm-process control to take advantage of the blessing without suffering from the curse

### WAVEGUIDES

unec

**UNIVERSITY**

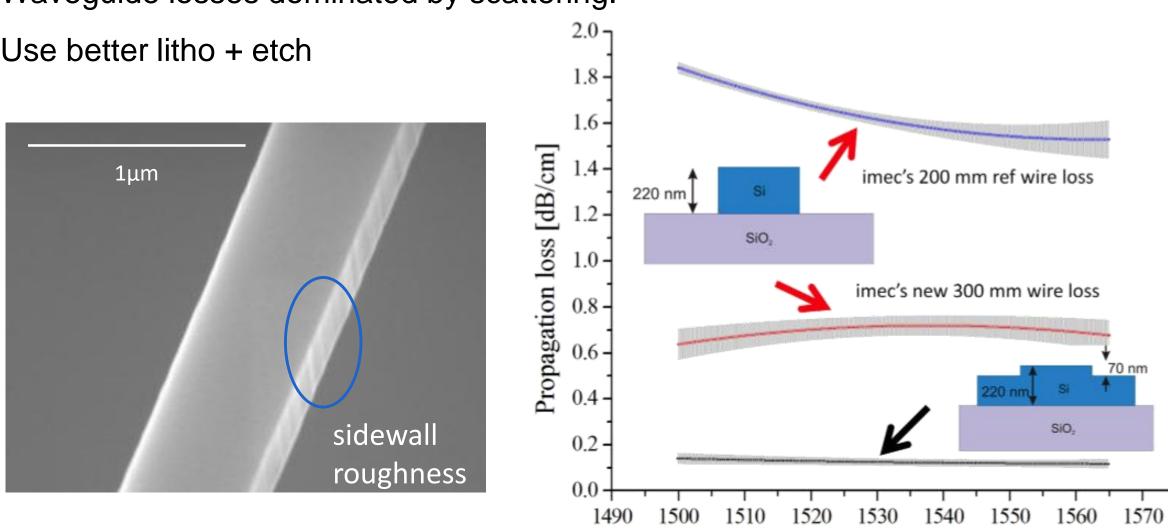

Waveguide losses dominated by scattering.

Use better litho + etch

Wavelength [nm]

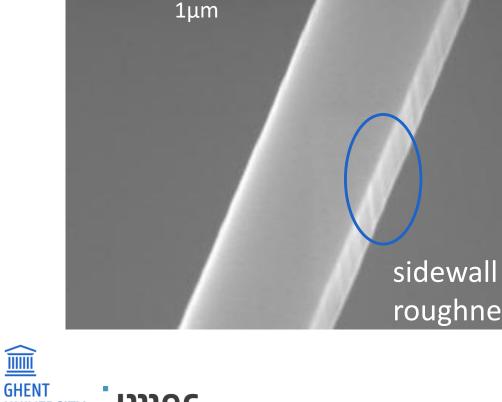

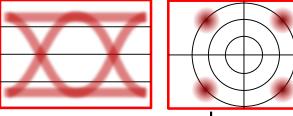

### COMPACT BENDS, TRANSITIONS, CROSSINGS

GHENT UNIVERSITY

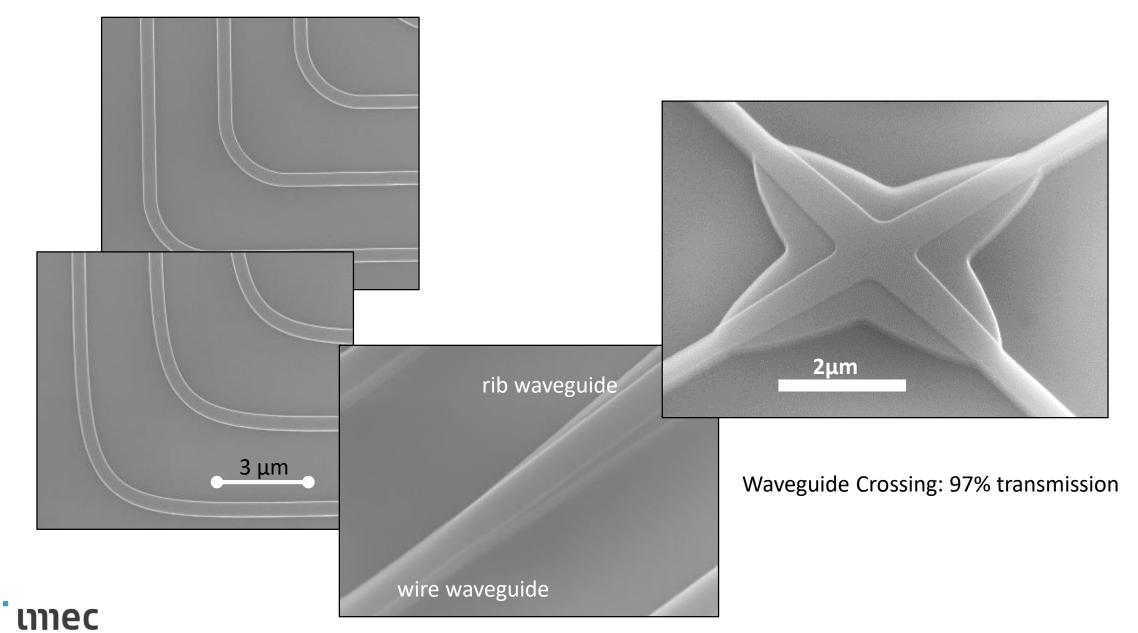

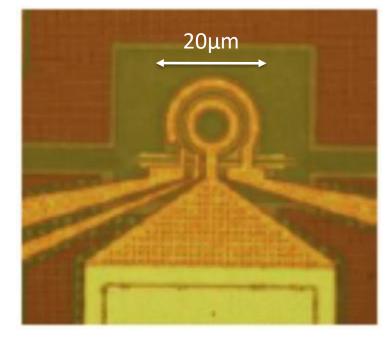

### FIBER-TO-CHIP COUPLING

Vertical fiber interface: allows easy on-chip testing

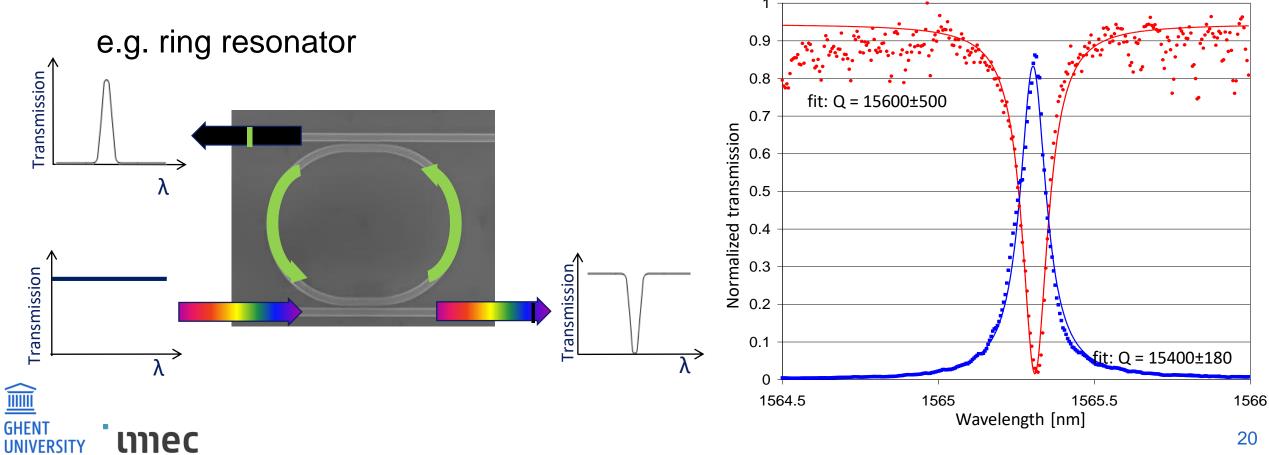

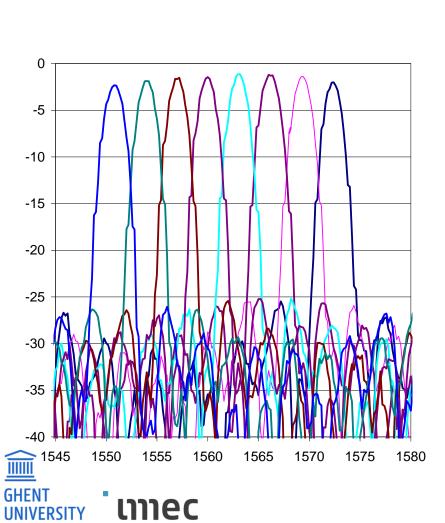

# WAVELENGTH FILTERING FUNCTIONS

Light is a wave: interference at the 100nm scale

- interferometers

- resonators

### WAVELENGTH FILTERING FUNCTIONS

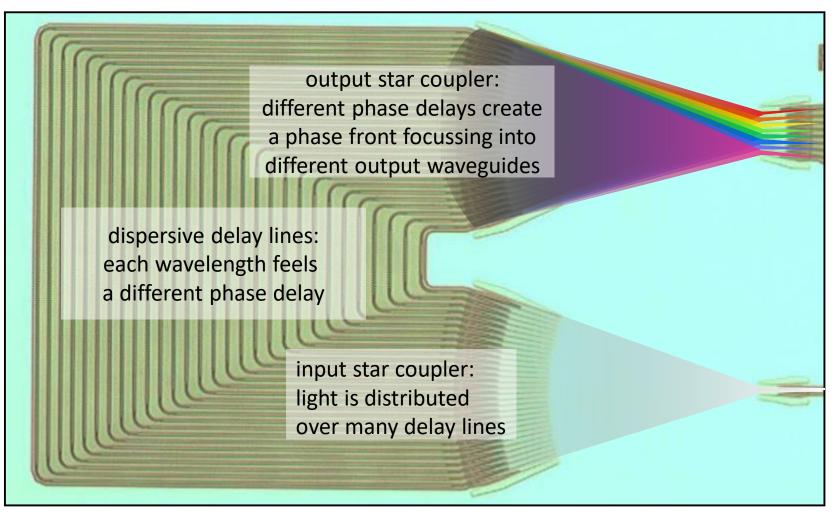

### Arrayed waveguide grating

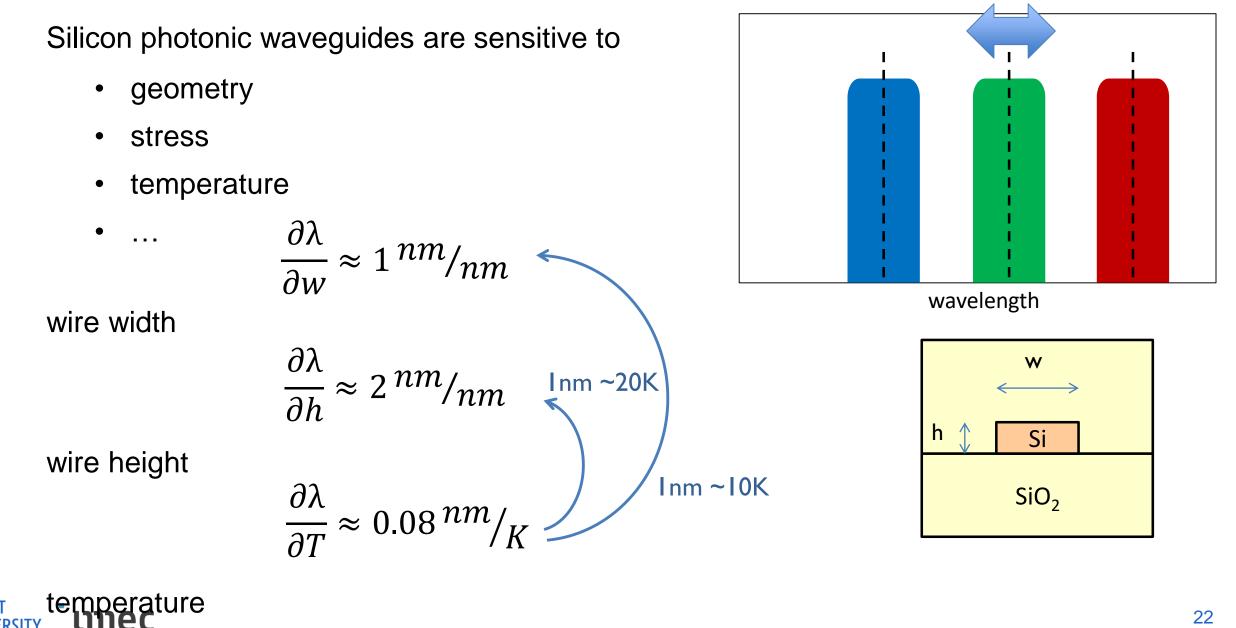

### SENSITIVITY OF SILICON PHOTONICS WAVELENGTH FILTERS

**GHENT**

UNIVERSITY

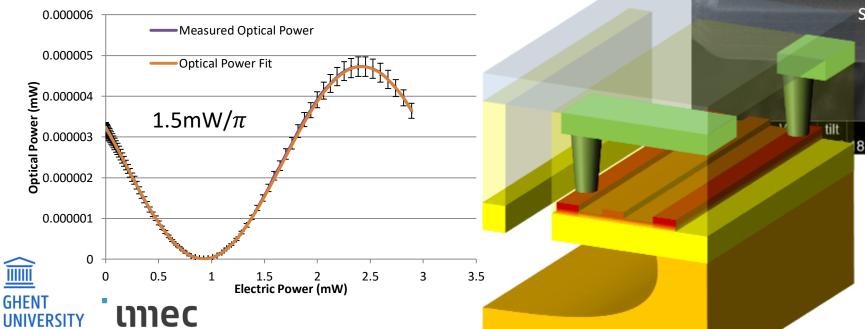

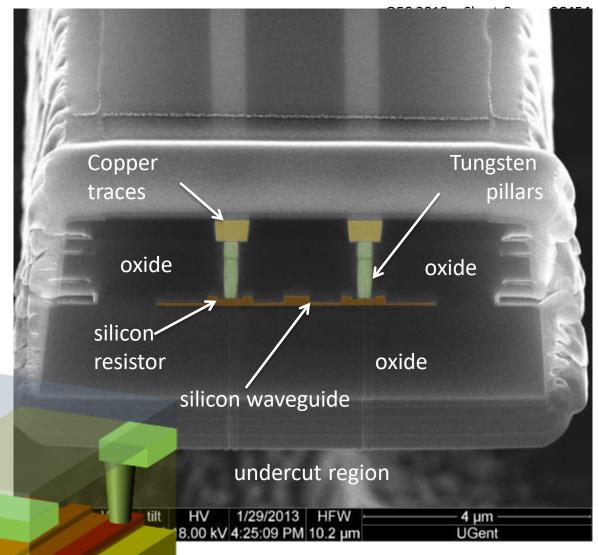

### INTEGRATED HEATERS FOR CONTROL

Different types of electrical resistors: metal, silicide, doped silicon

# Optional undercut to lower reduce thermal leakage.

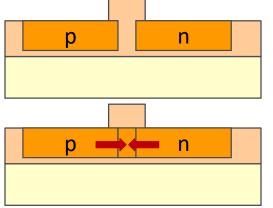

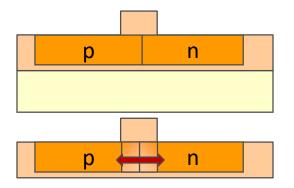

# ELECTRO-OPTIC EFFECT IN SILICON: INJECTION VS. DEPLETION

#### Carrier injection

- p-i-n diode in forward bias

- Inject carriers into waveguides

- Strong effect (many carriers)

- Slow effect (~1GHz)

Carrier depletion

- p-n diode in reverse bias

- Extract carriers from waveguide

- Weaker effect

- Fast effect (>40GHz)

Carrier accumulation

- Accumulation at oxide

- Similar to capacitor

- Fast

unec

**GHENT**

UNIVERSITY

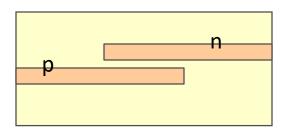

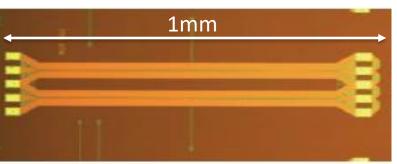

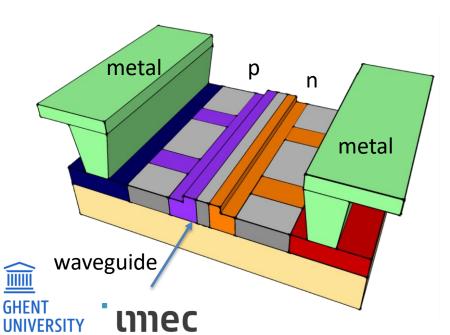

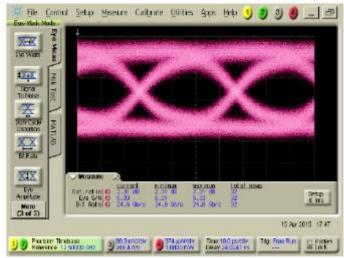

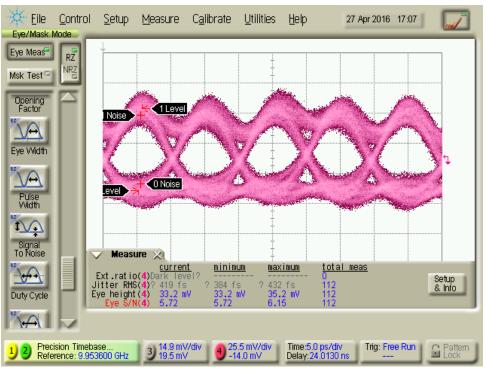

## **ELECTRICAL SIGNAL MODULATION**

Add doped junction to silicon waveguide: modulate refractive index

- travelling wave modulator

- ring resonator modulator

**25Gb/s, IVpp** Vbias= -0.2V, ER = 2.3dB, Q = 5.3, Opt. Power=13dbm, 1560nm, PRBS=2e31-1

56Gb/s, 2.5Vpp Vbias=-0.75V, ER=4dB, Q=4.2, PRBS=2e31-1

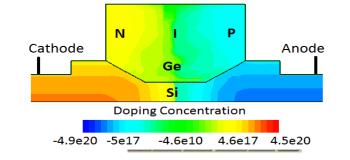

### **G**ERMANIUM ELECTRO-ABSORPTION MODULATOR

#### Advantages

- Uses existing Ge-detector technology

- Compact, optical BW > 35nm

•3dB BW > 40GHz

Next steps

**GHENT**

UNIVERSITY

•Ge  $\rightarrow$  SiGe to reach C-band

Ge-laser

unec

Gupta, S., et al. 50GHz Ge Waveguide Electro-Absorption Modulator Integrated in a 220nm SOI Photonics Platform. In *Optical Fiber Communication Conference* (Vol. 1, pp. 5–7) 2015.

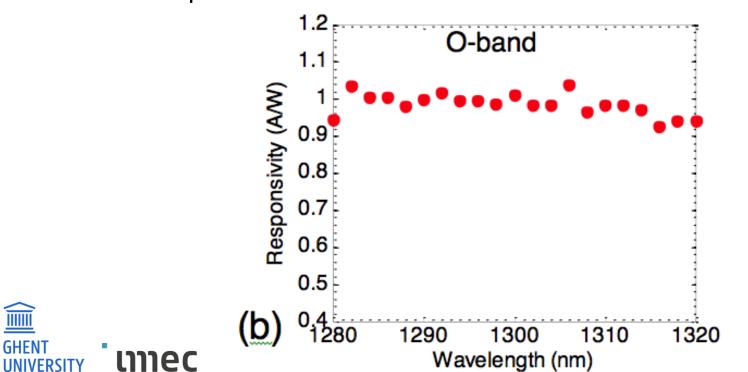

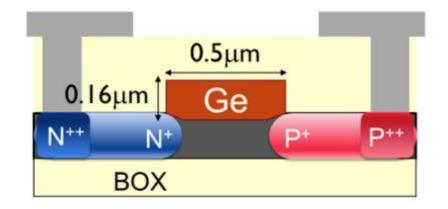

# **FAST AND EFFICIENT PHOTODETECTORS**

**Integrated Germanium Photodetectors**

- 1 A/W responsivity

- > 70 GHz bandwidth

- 3nA dark current \_\_\_\_

- 1 V operation

**GHENT**

### **INTEGRATION ON WAFER SCALE**

Compatible with CMOS processing

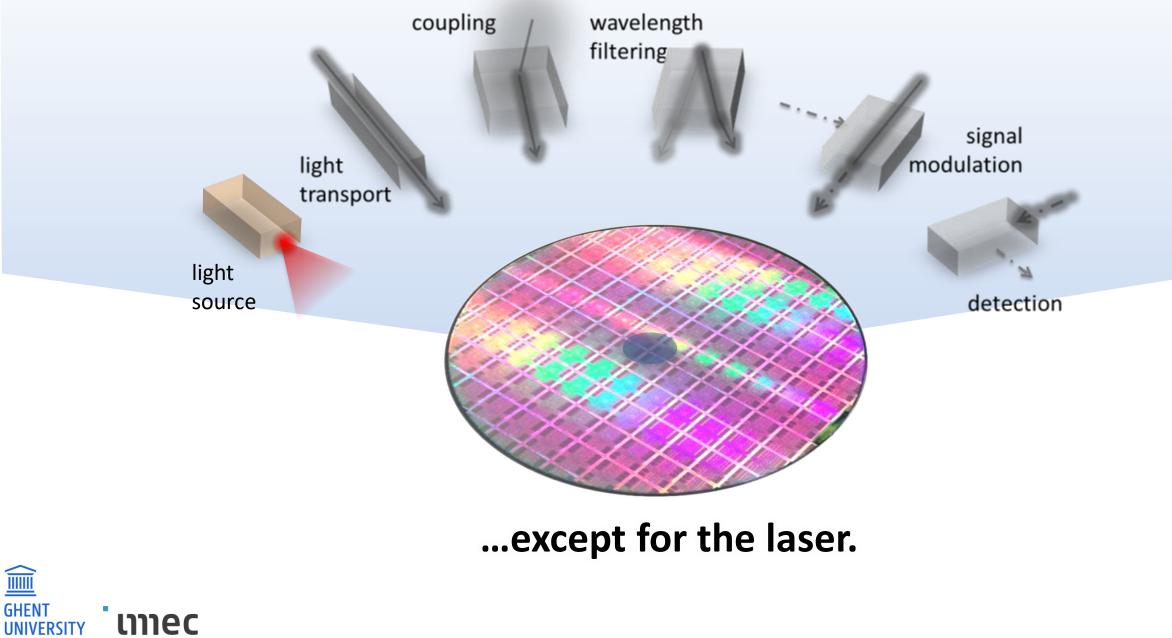

### ALL PHOTONIC FUNCTIONS ARE THERE...

ເກາຍc

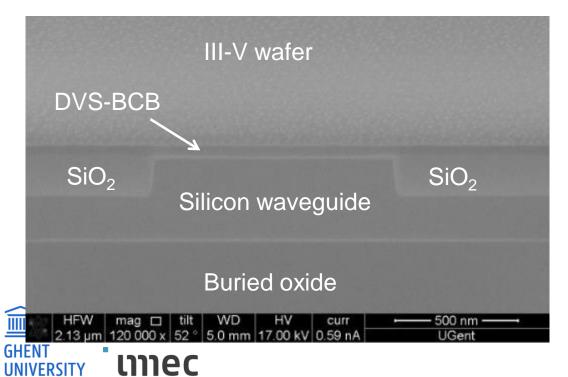

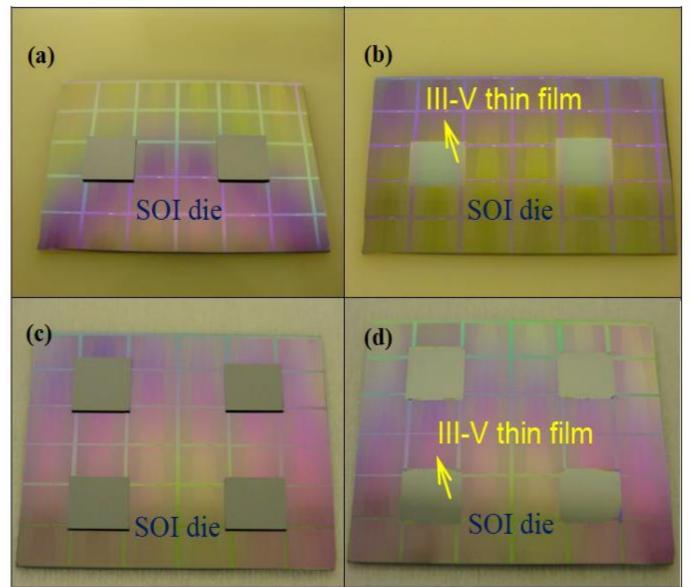

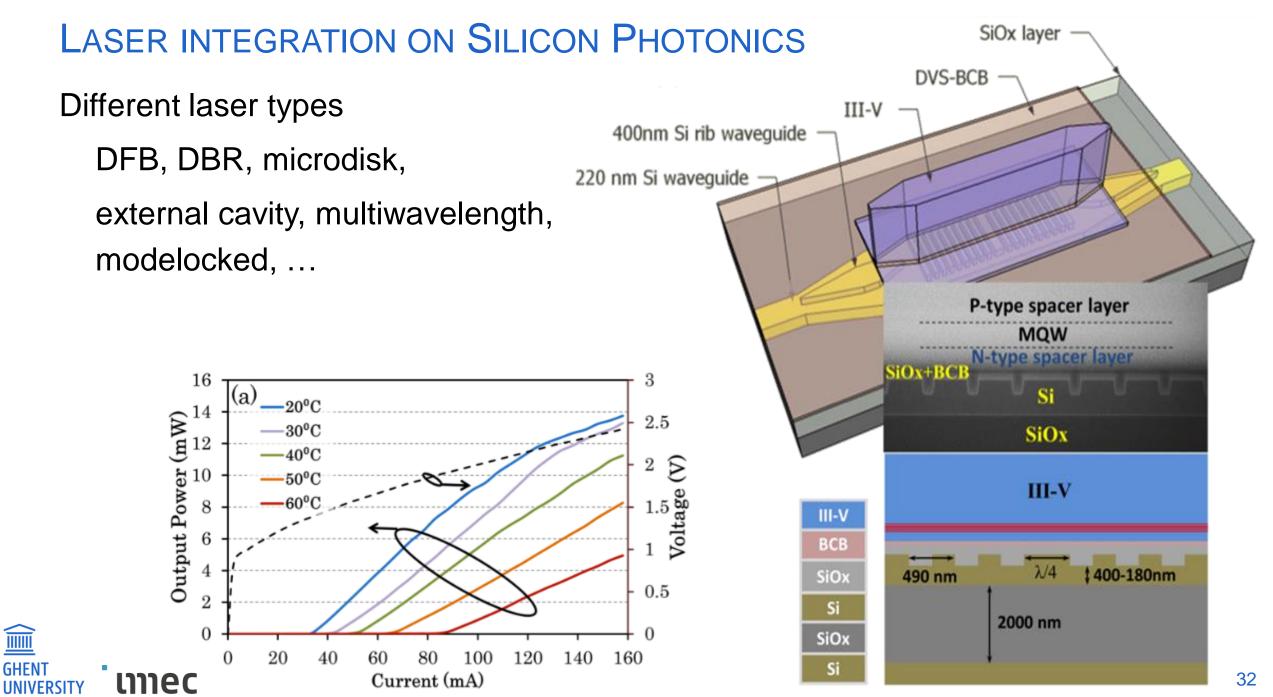

## LASER INTEGRATION ON SILICON PHOTONICS

# Transfer III-V laser material to the silicon Photonic chip

# SILICON PHOTONICS ENABLES LARGE SCALE PHOTONICS

### >10000 optical functions on a chip

optical guiding, filtering, detection and modulation

efficient fiber-chip coupling

external or integrated light sources

mec

GHEN

UNIVERS

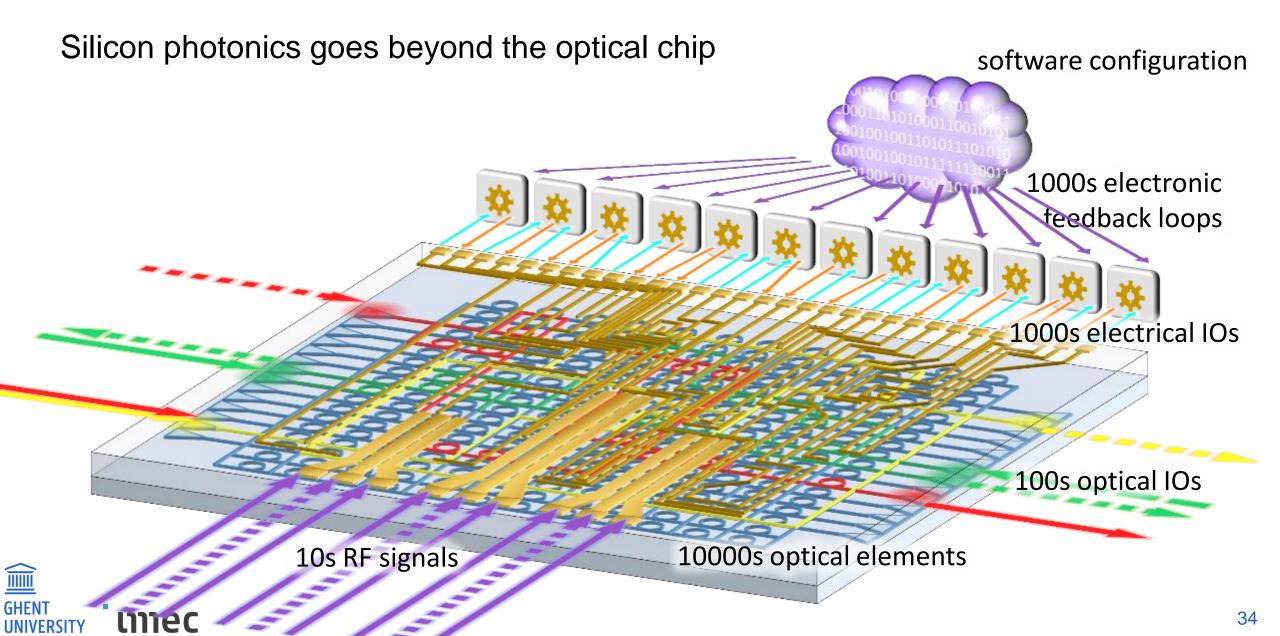

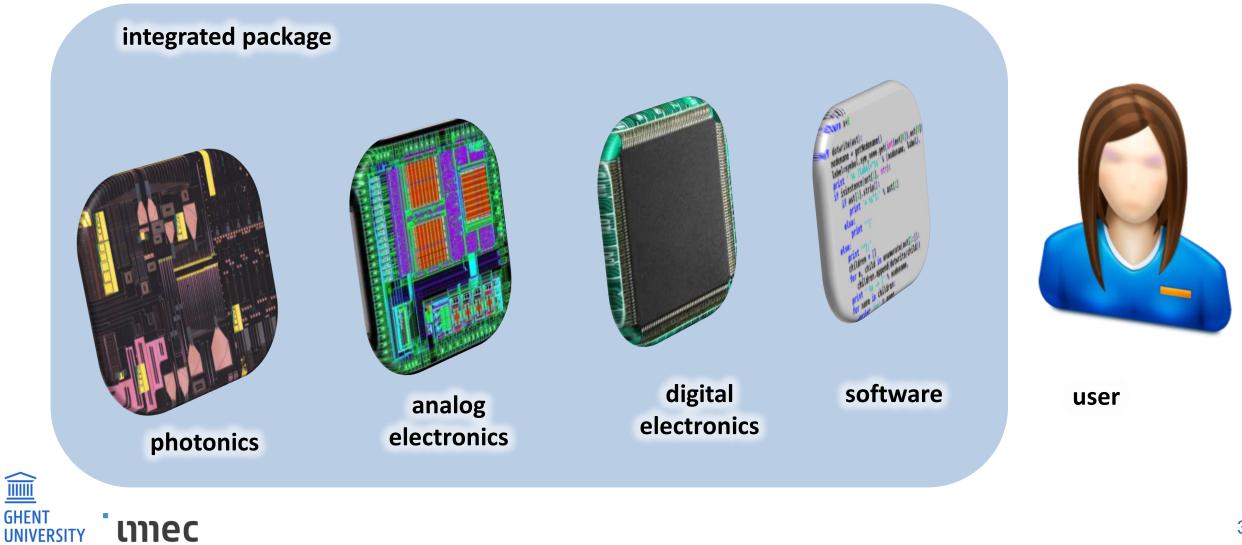

### MORE THAN JUST PHOTONS

# THE PHOTONIC CHIP IS JUST A PART OF THE SYSTEM

#### OFC 2018 – Short Course SC454 FIDER arrays

# PACKAGING TECHNOLOGY

- Combining photonics and electronics

- Fiber interfaces

- RF connections

- Thermal and mechanical

unec

**GHEN1**

UNIVERSITY

shielded packages

# FABLESS SILICON PHOTONICS

Many fabless Silicon Photonics companies have emerged

- from direct collaboration with fabs (Luxtera, ...)

- starting from MPW (Caliopa, Genalyte, Acacia)

Established players are also partnering

• e.g. Finisar with ST

**1ec**

• Many keep their fab a secret

How to enter as a new (fabless) startup?

### Small building blocks $\rightarrow$ Large circuits

µm-scale building blocks

cm-scale chips

**Photonics**

Very Large Scale Integration (VLSI)

thousands – millions components

### COMPLEXITY AS AN ENABLER

### **Integrated Electronics**

GHENT

UNIVERSITY

unec

- billions of digital gates: unprecedented logic performance

- millions of analog transistors: unprecedented control

- (even with imperfect components: enabled by design!)

**Integrated Photonics (Silicon Photonics)**

- technological potential of 10000+ photonic elements on a chip

- not even scratched the surface of what this could do

# PHOTONIC CIRCUIT DESIGN

# **ENABLING COMPLEXITY IN PHOTONICS**

unec

Industrial PIC technology platforms (Si, InP, ...)

- demonstrations of sensors, spectrometers, ...

- commercial products

But: fairly simple circuits ~ 1970s ICs

### More complexity is enabled by design methods

- Design capture: translating ideas to circuits

- Circuit simulation (electrical+photonic)

- Variability analysis on circuits

- Yield prediction and improvement

# COMPLEX CIRCUITS $\neq$ COMPLICATED BUILDING BLOCKS

You can do a lot with a few building blocks

Electronics: Transistors, Resistors, Diodes, ... Photonics: Waveguides, Directional couplers, ...

**Complexity emerges from connectivity**

But you need to support complexity

- Accurate models

- Variability

- Parasitics

nec

GHEN

### DESIGNING PHOTONIC INTEGRATED CIRCUITS

Can we learn from electronic ICs?

- Millions of analog transistors

- Billions of digital transistors

- Power, timing and yield

- First time right designs

unec

**GHENT**

UNIVERSITY

- Very mature Electronic Design Automation (EDA) tools!

- A well established design flow

Can we repurpose this for photonics?

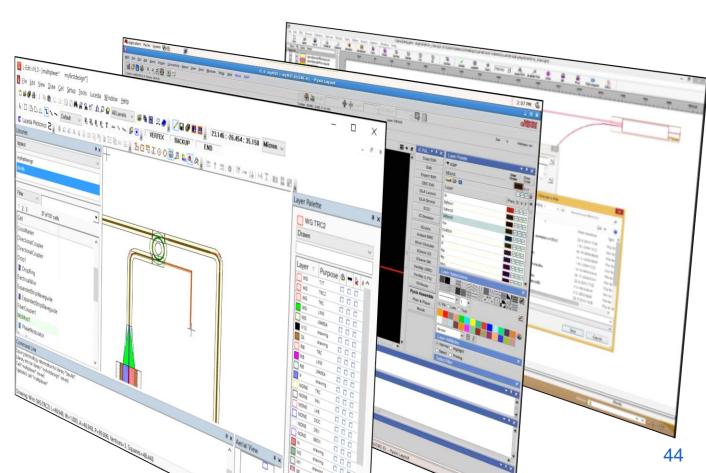

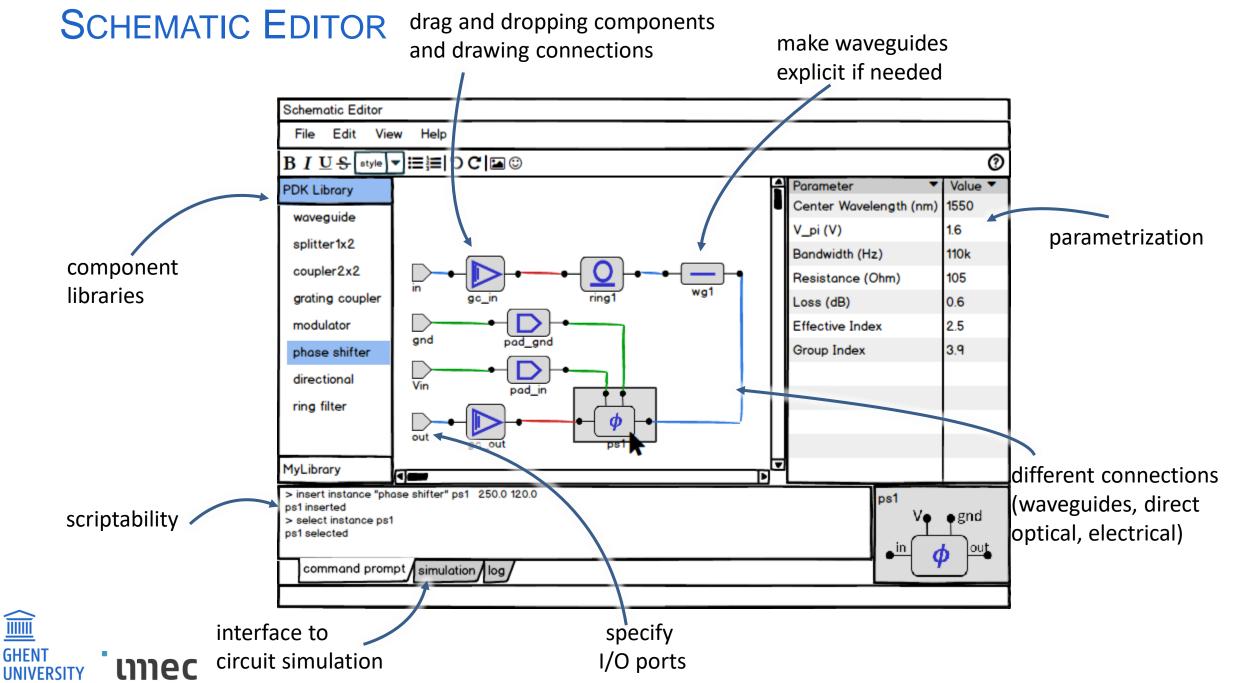

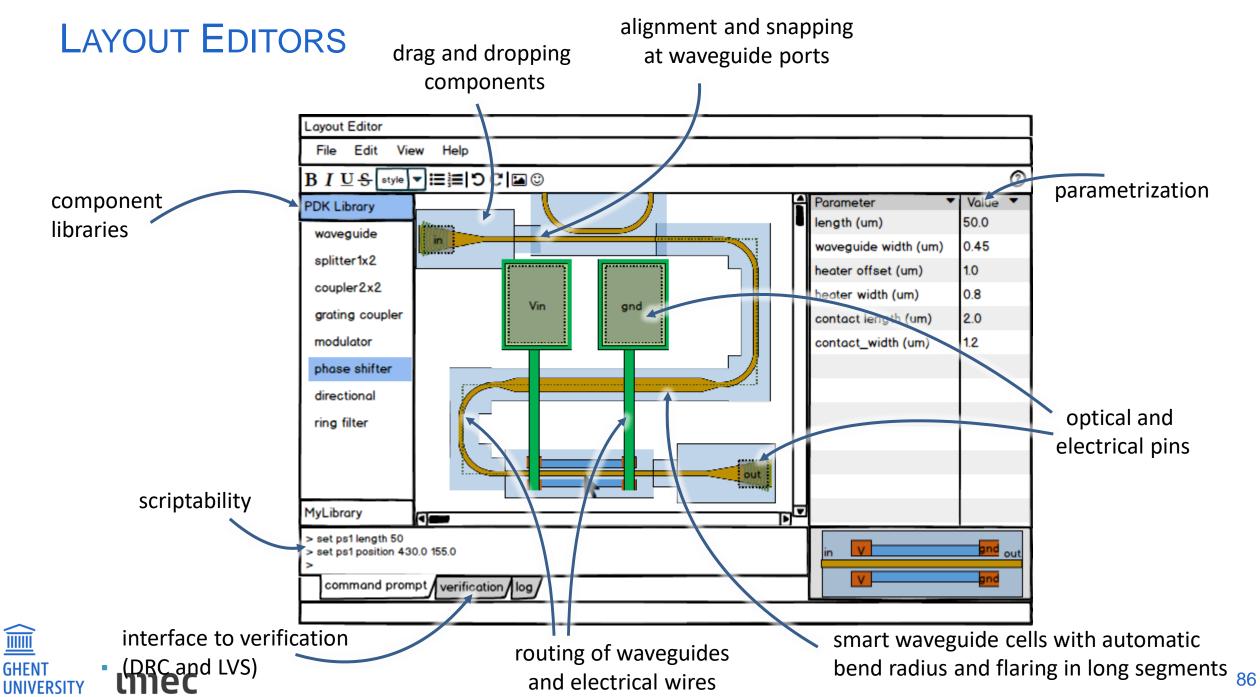

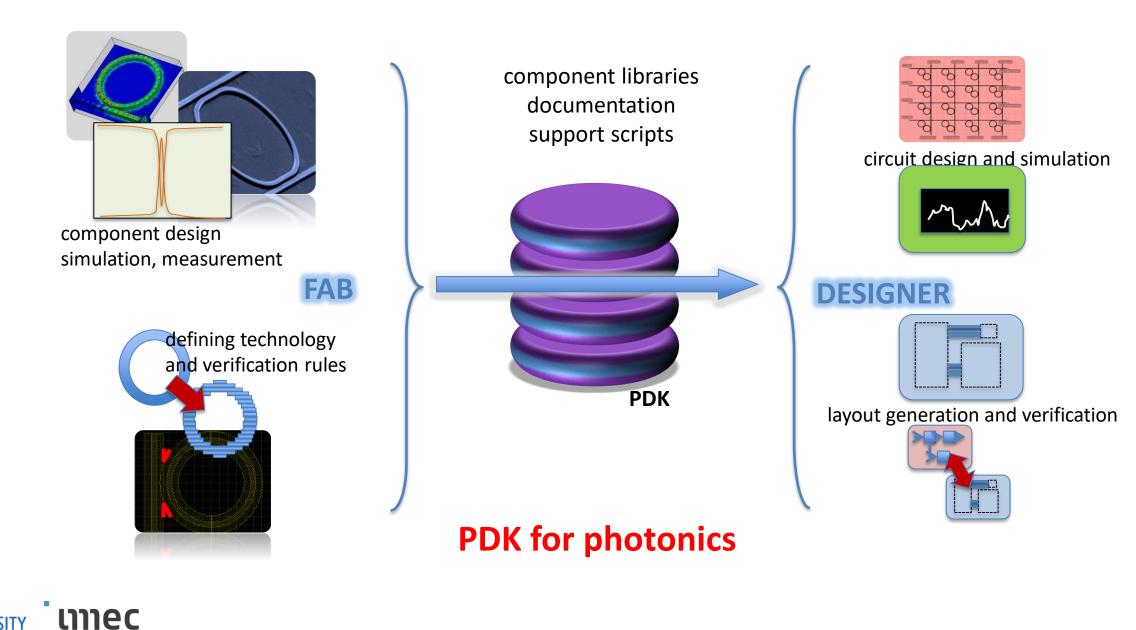

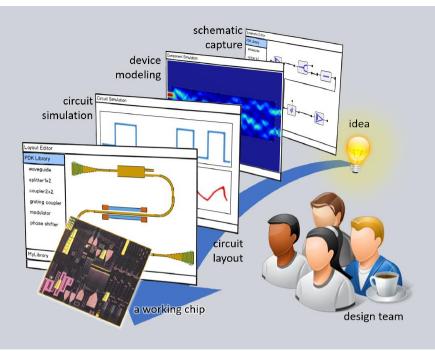

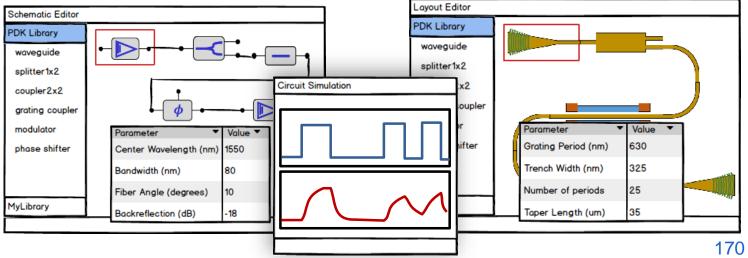

# DESIGN ENVIRONMENTS ARE EMERGING

Combinations of Photonics Design and EDA

Physical simulation combined with circuit design

Physical and functional verification

First PDKs with basic models

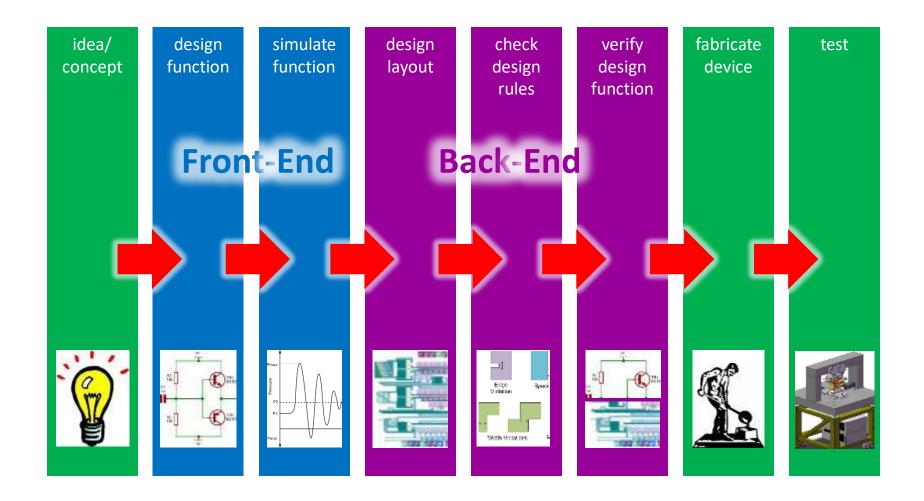

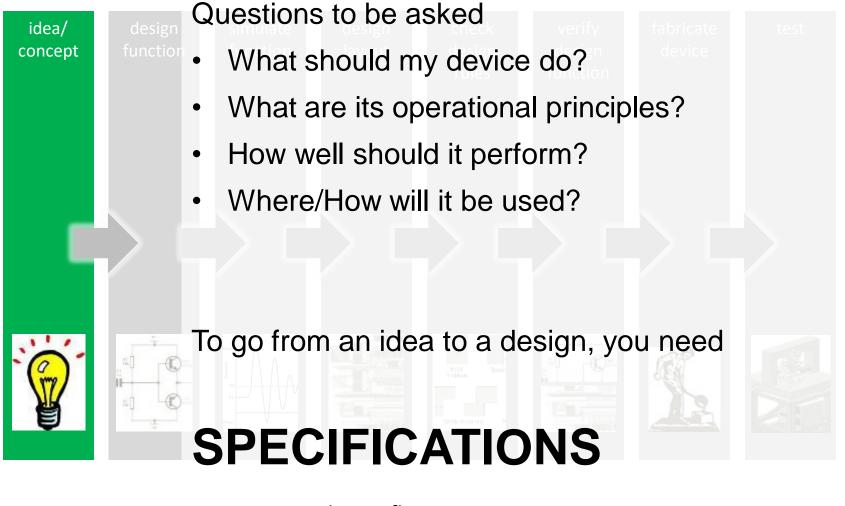

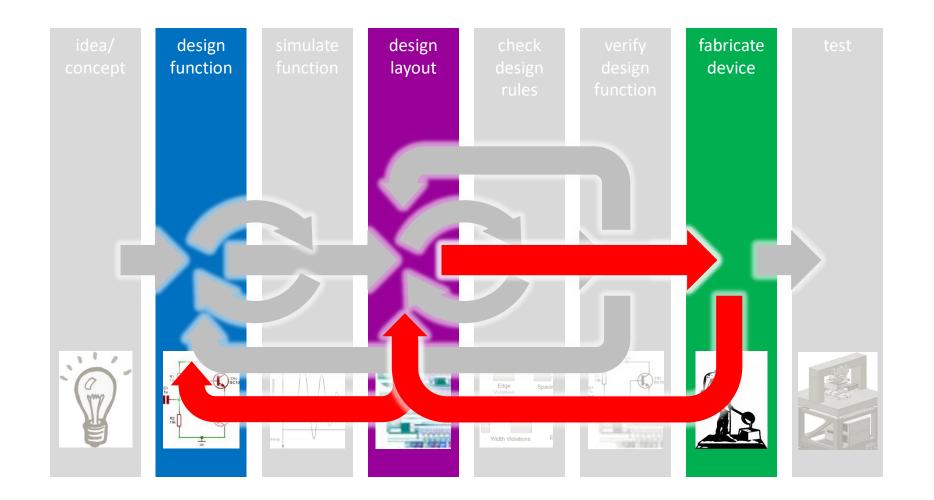

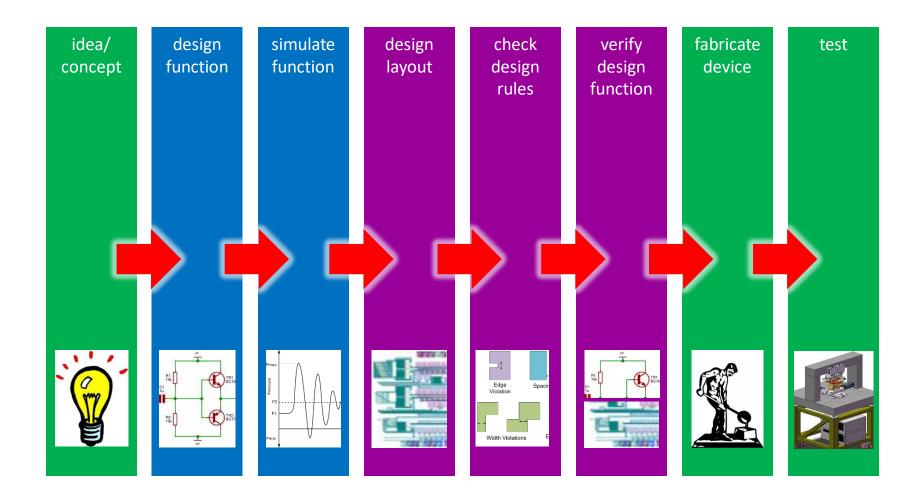

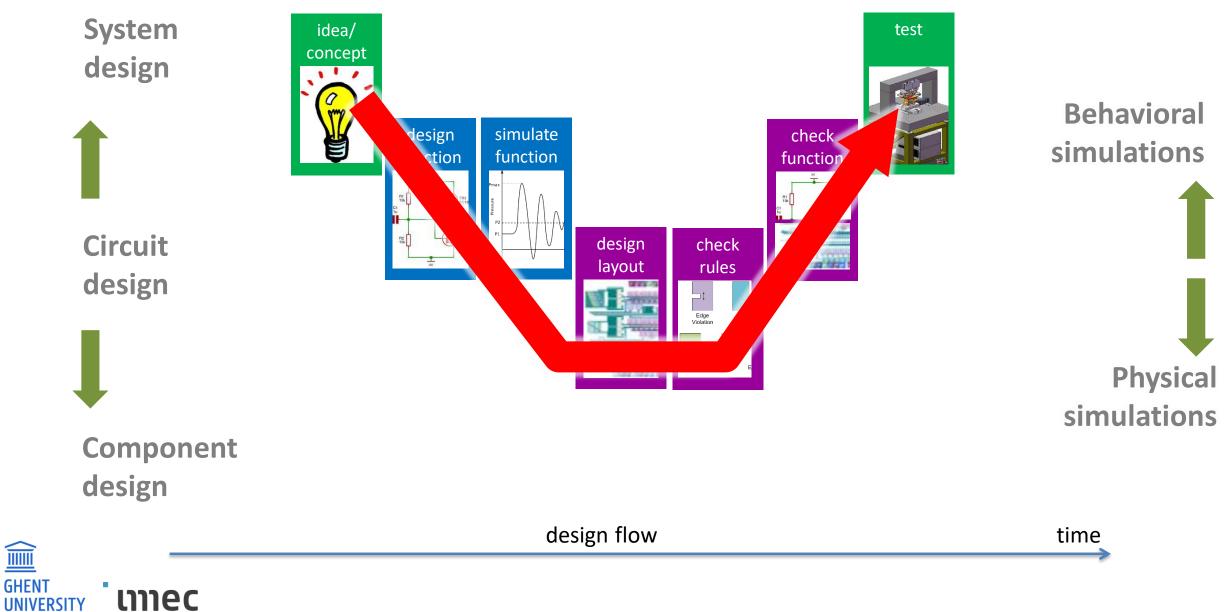

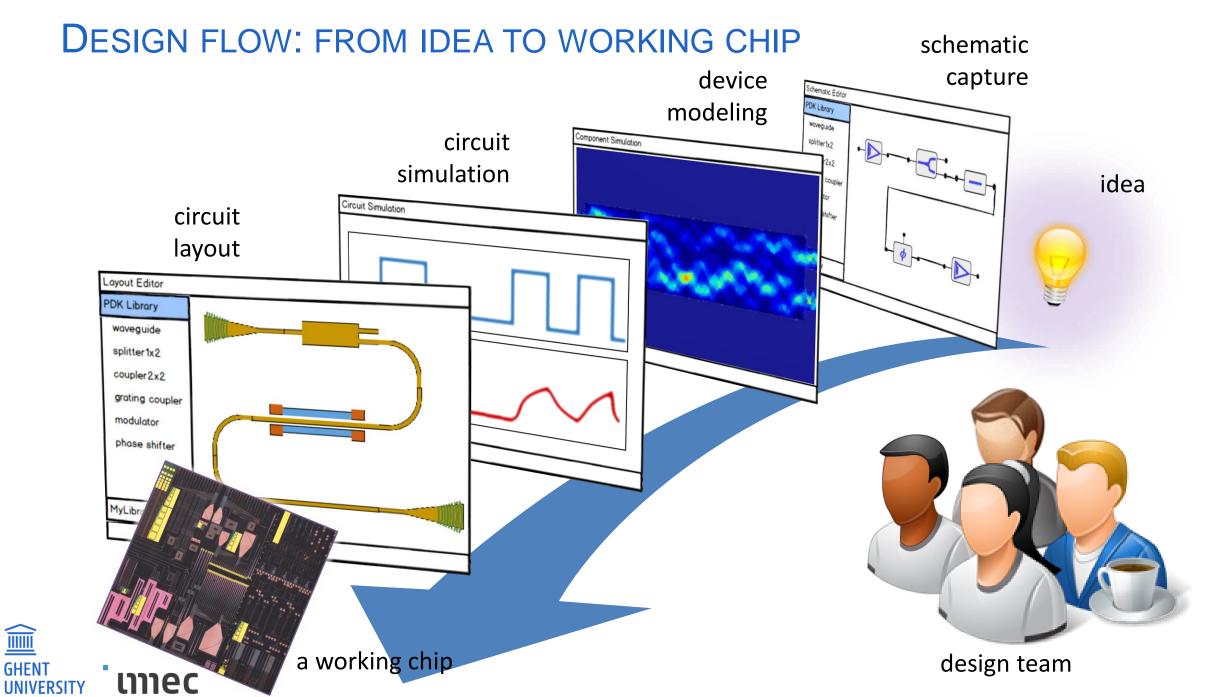

#### WHAT IS A DESIGN FLOW?

<sup>66</sup> Design is the creation of a plan or convention for the construction of an object or a system??

**Design Flow**

<sup>6</sup> <sup>6</sup> a repeatable pattern of activity, usually involving multiple tasks with a specific set of outcomes??

#### WHAT IS THE PURPOSE OF A DESIGN FLOW?

to translate an idea into a WORKING chip.

#### A TYPICAL DESIGN CYCLE

**IIII** GHENT

UNIVERSITY

umec

design flow

49

#### A GREAT IDEA?

design flow

time

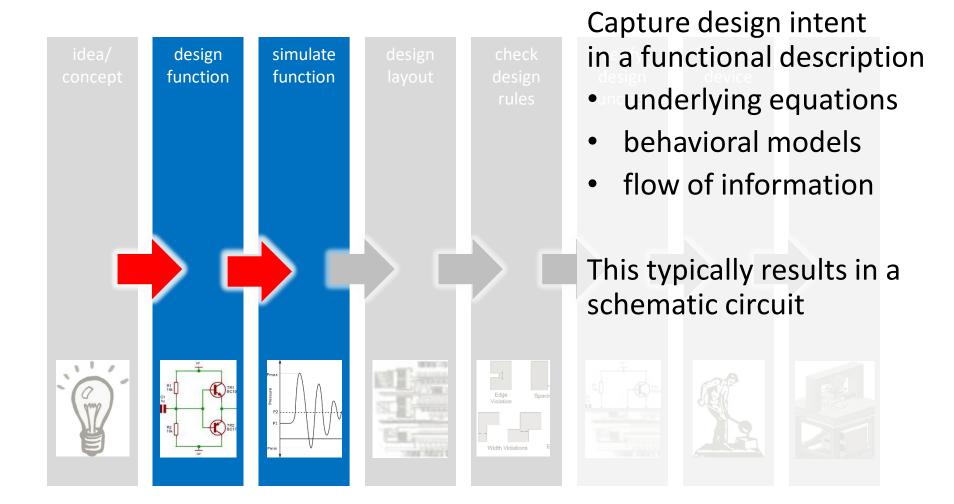

# DESIGN CAPTURE AND SIMULATION

design flow

time

# **DESIGN CAPTURE**

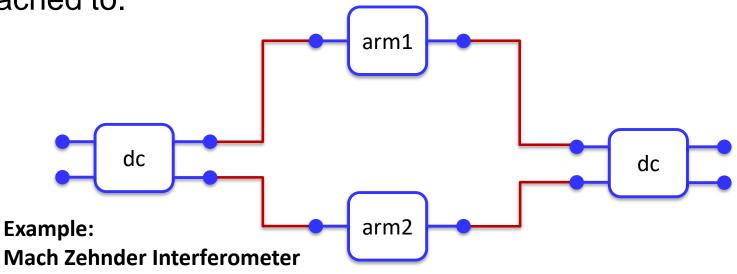

Select/construct functional blocks Connect them together

#### • Netlist:

list of connections ("Nets") and which components the nets are attached to.

• Schematic:

unec

**GHEN1**

UNIVERSITY

graphical representation of a netlist, with placements

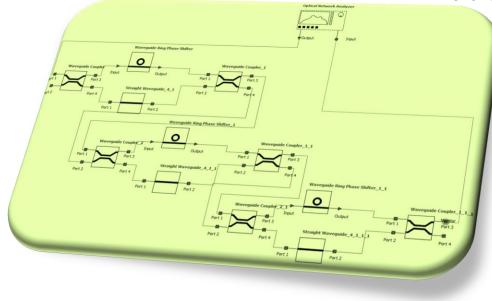

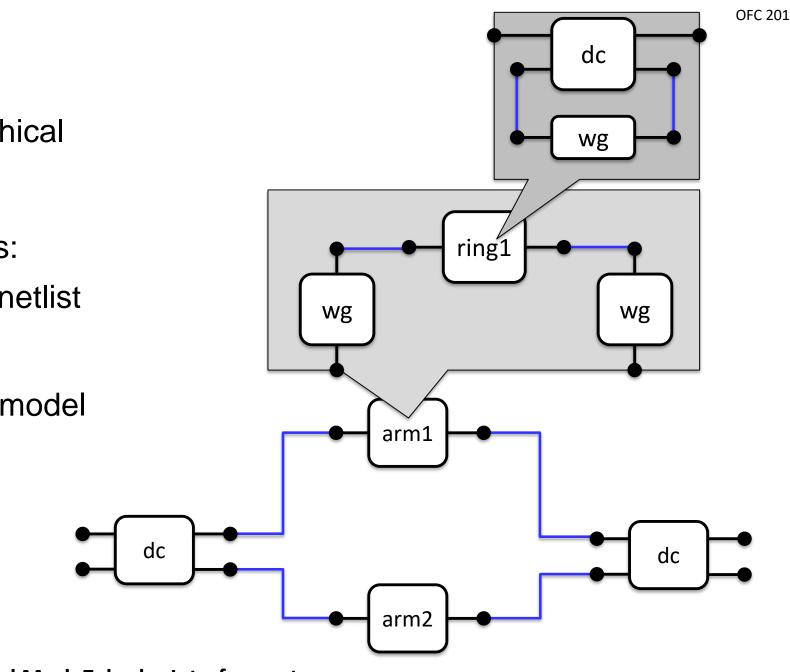

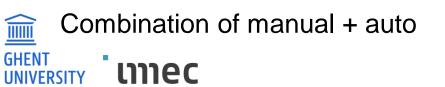

#### HIERARCHY

#### Netlists are hierarchical

- Hierarchical cells: contain another netlist

- Atomic cells: contain a circuit model

umec

**IIII** GHENT

UNIVERSITY

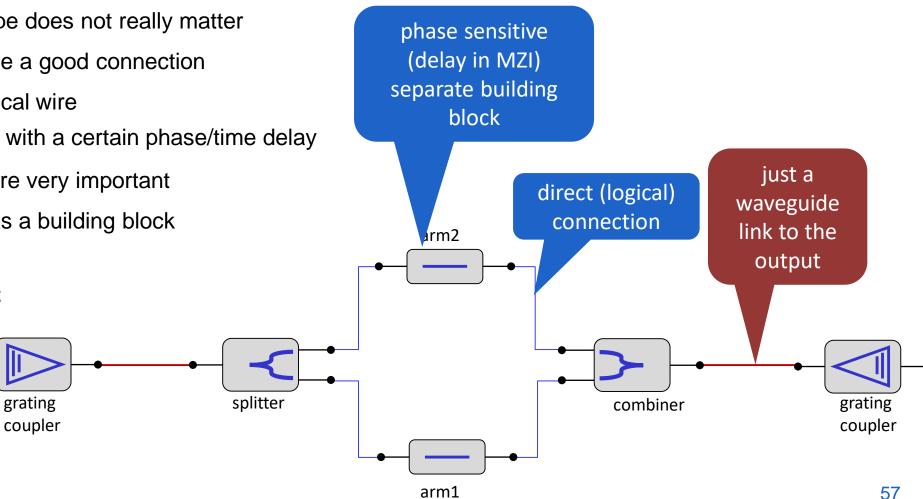

# WAVEGUIDES IN PHOTONIC SCHEMATICS

#### What are waveguides?

- Simple connections between building blocks ٠

- the length and shape does not really matter ٠

- it should just provide a good connection ٠

- similar as an electrical wire ٠

- Functional building blocks with a certain phase/time delay •

- length and shape are very important ٠

- should be treated as a building block ٠

#### The distinction is important

unec

**GHENT**

UNIVERSITY

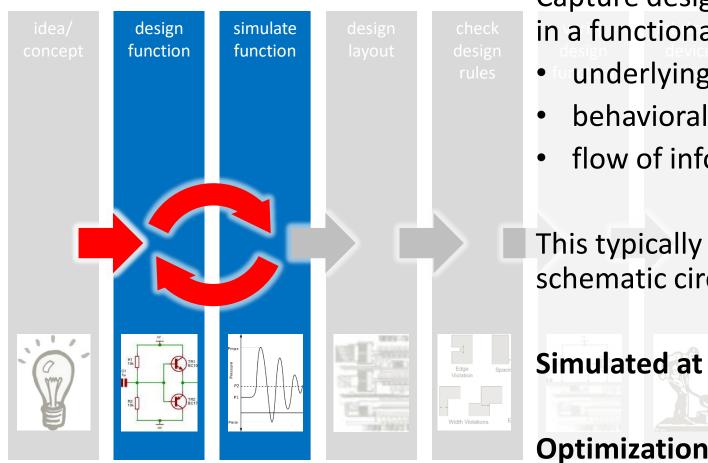

# **DESIGN CAPTURE AND SIMULATION**

Capture design intent in a functional description

- underlying equations

- behavioral models

- flow of information

This typically results in a schematic circuit

Simulated at an abstract level

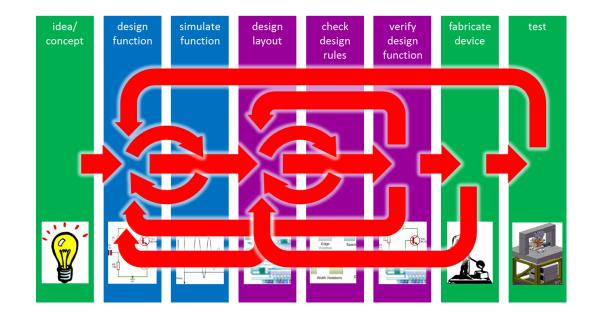

#### **Optimization:** an iterative process

**GHENT** nnec UNIVERSITY

design flow

time

# COMPONENT SIMULATION $\neq$ CIRCUIT SIMULATION

#### **Physical models**

Accurate, slow

Based on actual geometries

Best model = reality

#### **Circuit simulations**

Approximate, fast

Based on functional description

behavioural models

#### MODELS

Should allow simulation in a larger circuit

- based on equations

- based on measurement data

- based on EM simulations

Photonics: Nothing really standardized

- No standardized simulation method

- No standard model description

- No standard signals

mec

GHEN

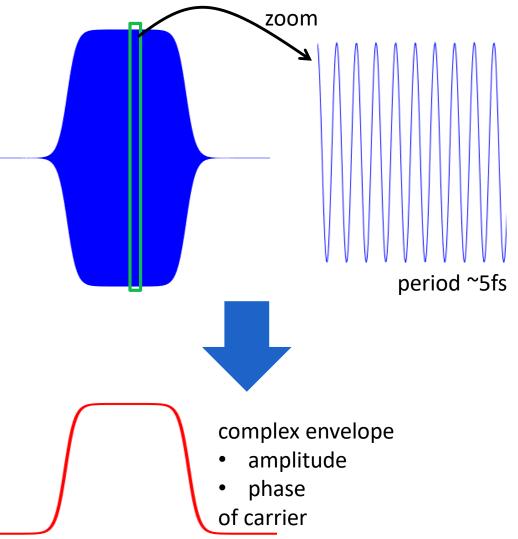

# OPTICAL VS. ELECTRICAL CIRCUIT SIMULATION

optics = electric... at very high frequency

- ultra-small time steps (fs)

- ultra-long simulations (10<sup>12</sup> time steps)

- high-bandwidth signals (200THz)

impractical.

mec

**GHEN1**

UNIVERSITY

Solution: analytic signal

= complex amplitude on carrier

# PHOTONIC CIRCUIT SIMULATIONS

Same as electronics? No. Photonics does not fit in Spice

#### Effort-flow systems

| ElectricalVoltageCurrentFluidicPressureFlowThermalTemperatureHeat Flow*MechanicalForceMotionPhotonic?E-fieldH-field |            |             |            |

|---------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|

| ThermalTemperatureHeat Flow*MechanicalForceMotion                                                                   | Electrical | Voltage     | Current    |

| Mechanical Force Motion                                                                                             | Fluidic    | Pressure    | Flow       |

|                                                                                                                     | Thermal    | Temperature | Heat Flow* |

| Photonic? E-field H-field                                                                                           | Mechanical | Force       | Motion     |

|                                                                                                                     | Photonic?  | E-field     | H-field    |

Not the best formalism for photonics (too high frequency, much more than an RF wave)

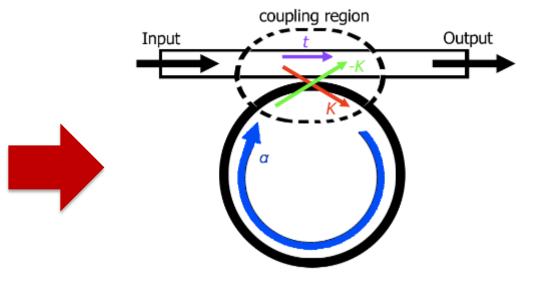

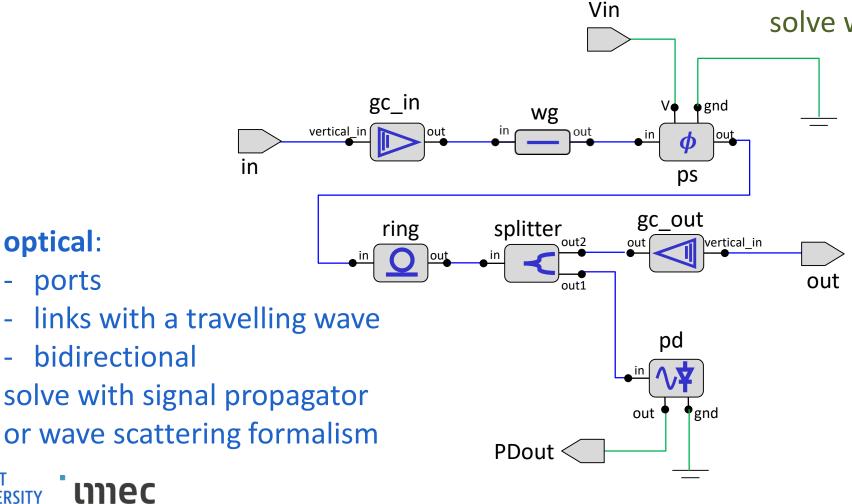

# Wave scattering formalism ≠ Effort Flow Formalism

#### electrical and optical is not the same

optical:

GHENT

UNIVERSITY

ports

#### electrical:

- nets with a voltage potential

- current flowing through terms

solve with SPICE

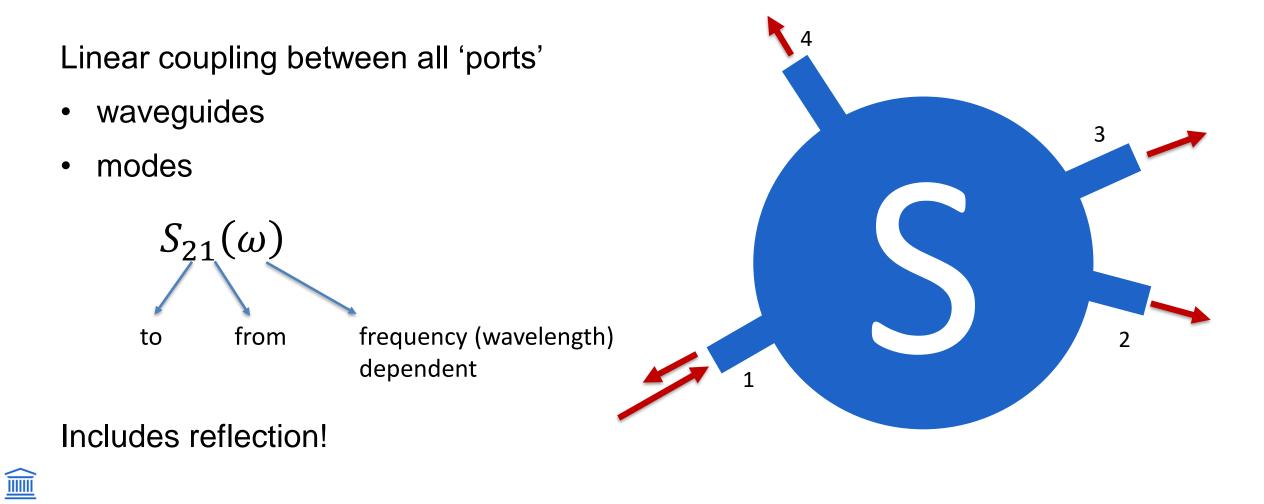

# LINEAR PHOTONICS: SCATTER MATRICES

Generalized reflections of a propagating wave

**GHENT**

UNIVERSITY

unec

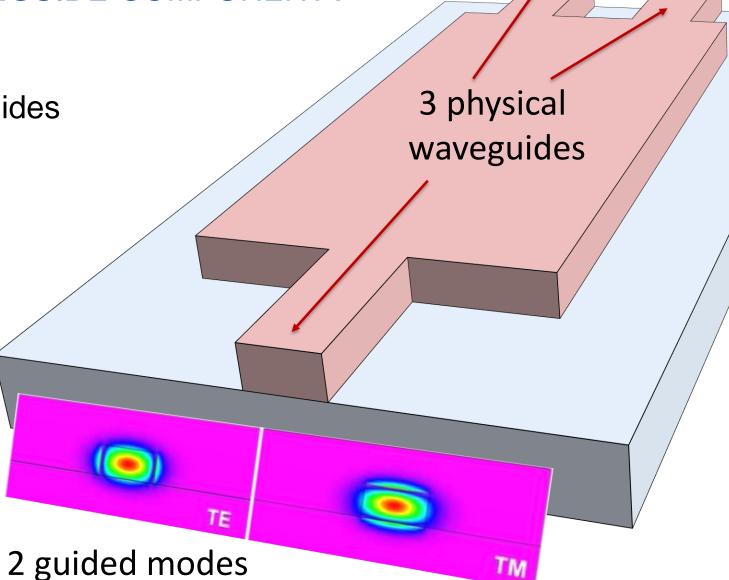

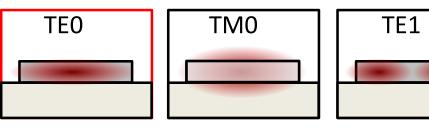

# WHAT IS A PORT OF A WAVEGUIDE COMPONENT?

#### Orthogonal states

- Physically separated waveguides

- Each mode in the waveguide

Example: 6 "ports" 6x6 S-matrix

In practice:

unec

**GHEN**

UNIVERSITY

Only use the relevant modes (rest is "loss")

## **FREQUENCY DOMAIN OPTICAL CIRCUIT SIMULATOR**

#### Frequency domain

- Linear systems ٠

- Described by scatter matrices (S-parameters) ٠

Circuit is solved as a single matrix (similar as RF)

# **FREQUENCY DOMAIN SIMULATIONS**

Frequency domain simulations are very useful for calculating

- **Insertion** losses ullet

- **Backreflections** ullet

- Dispersion (wavelength dependent behavior) ullet

- Wavelength filter response ullet

and can also be extended to model

Slowly varying effects •

mec

Certain optical nonlinearities ullet

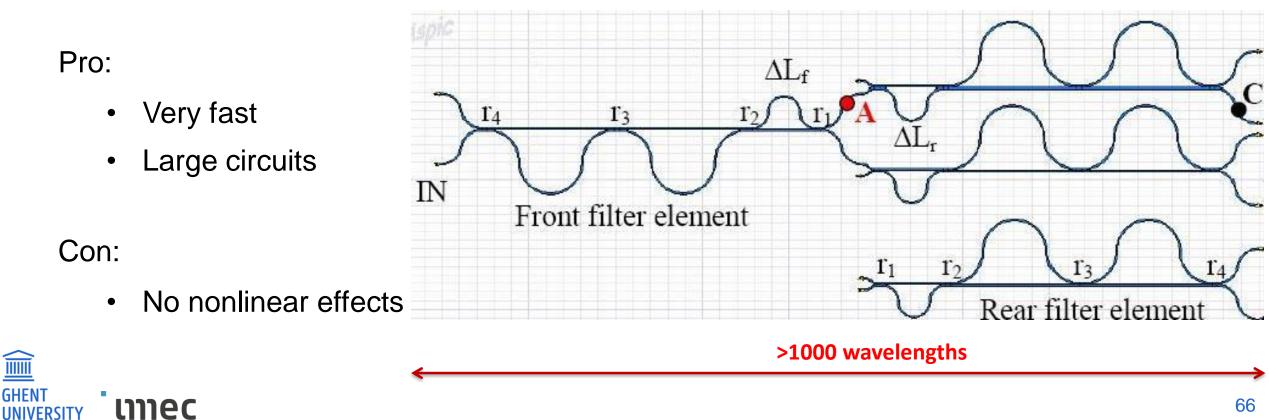

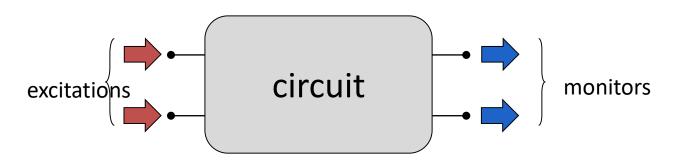

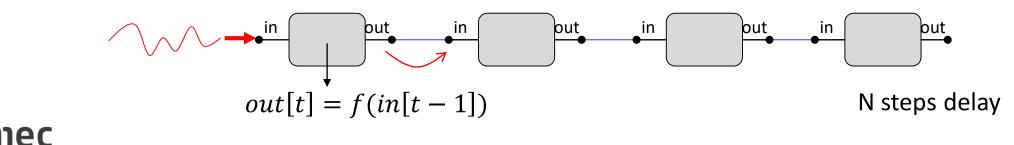

# TIME DOMAIN OPTICAL CIRCUIT SIMULATION

#### Calculate time response of a circuit

- to a stimulus (or combination of excitations)

- at certain output monitors

- using discrete time steps

#### Pro:

• Fast

mec

• Large circuits

#### Con:

GHENT

UNIVERSITY

- Slower than frequency domain

- Only response to specific stimulus

# TIME-DOMAIN OPTICAL CIRCUIT SIMULATION

#### Nodes

- connected by signal lines (bidirectional)

- an internal state

- an algorithm to calculate output from inputs and internal state (differential equations, coupled-mode theory, custom code)

every time step, in each node:

- Input signals of last time step are read

- Internal state is updated

- Output signals are generated

**GHENT**

UNIVERSITY

# 71

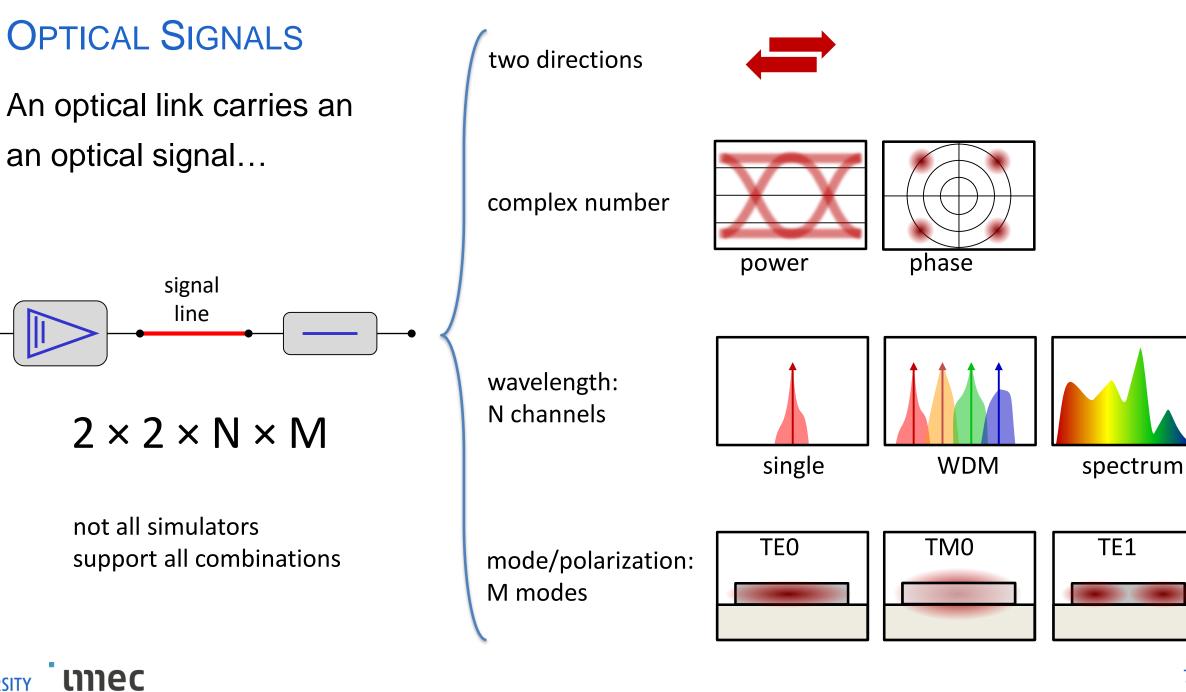

# **OPTICAL SIGNALS: EXAMPLE**

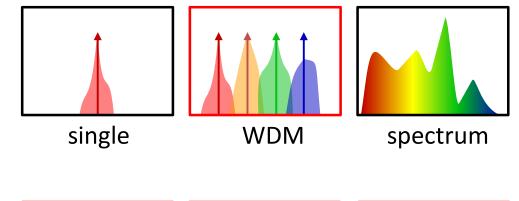

#### Example: Single- $\lambda$ link

- One direction  $\bullet$

- One wavelength •

- **On-off-keying:** power •

- One mode: TE  $\bullet$

unec

**GHENT**

UNIVERSITY

$1 \times 1 \times 1 \times 1$

not all simulators support all combinations

mode/polarization: M modes

two directions

complex number

wavelength:

N channels

# Optical Signals: Example

# two directions

## Example: WDM bidirectional link

- two directions

- QPSK modulation: phase

- 32 wavelength channels

- one mode

unec

**GHENT**

UNIVERSITY

$2 \times 2 \times 32 \times 1$

complex number

wavelength:

N channels

power

phase

mode/polarization: M modes

#### **OPTICAL SIGNALS: EXAMPLE** two directions

### Example: DWDM multimode link

- two directions

- QAM64 modulation: phase

- 512 wavelength channels

- 4 modes

unec

**GHENT**

UNIVERSITY

$2 \times 2 \times 512 \times 4$

complex number

wavelength:

N channels

power

mode/polarization: M modes

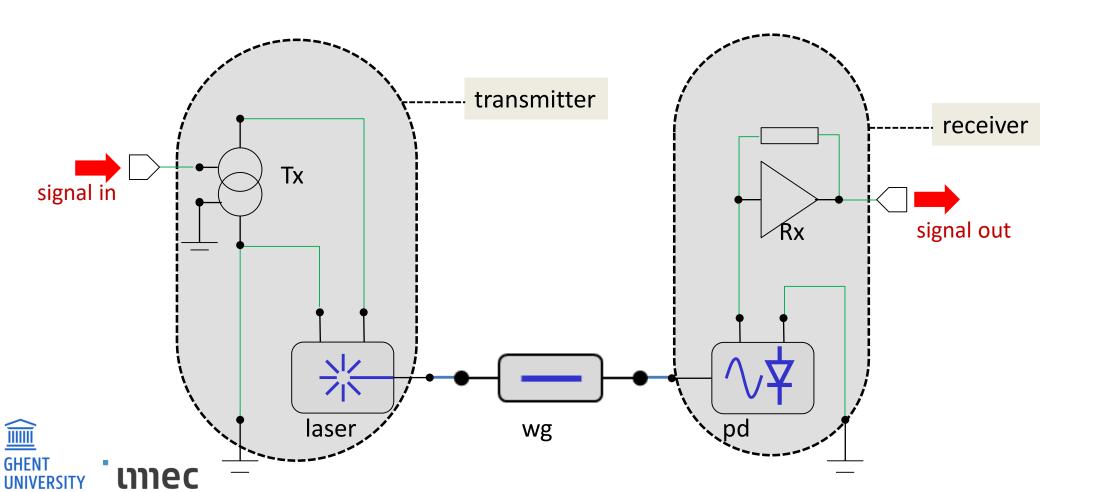

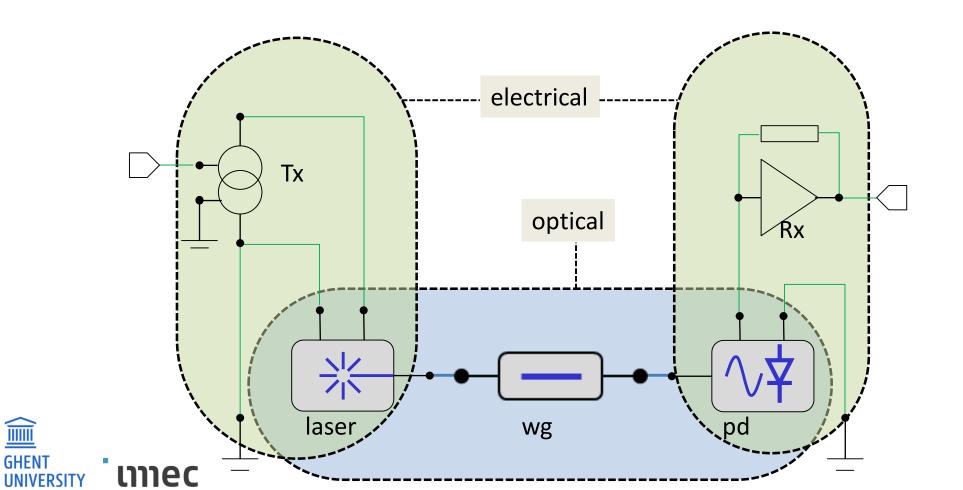

Real system: photonics + electronics

Example: optical link

Circuit has optical and electrical parts:

Some components overlap

75

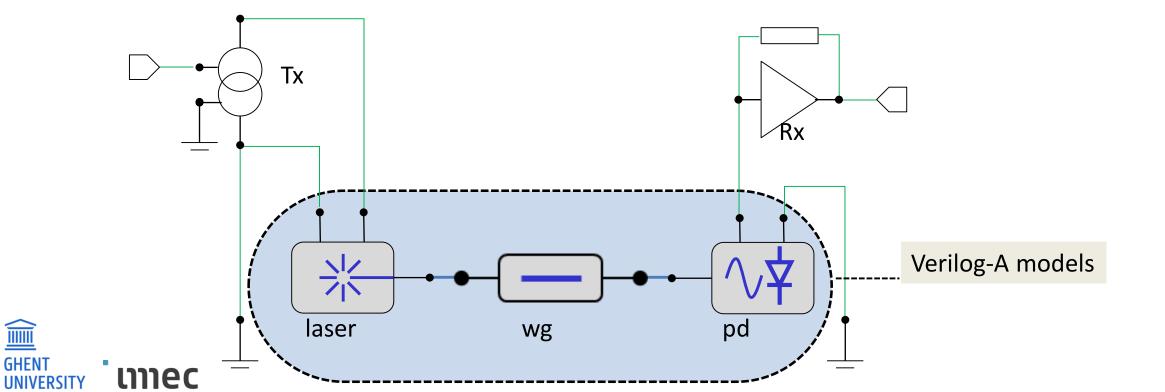

Simulating everything in electrical simulator (SPICE – MNA)

- Use native, verified models for electronics

- Build Verilog-A models for photonics

## **PHOTONICS IN VERILOGA**

Encode time signals as 'analytical' signals (complex numbers) (a)

Bus of two lines for bidirectionality

Modulation on an optical wavelength

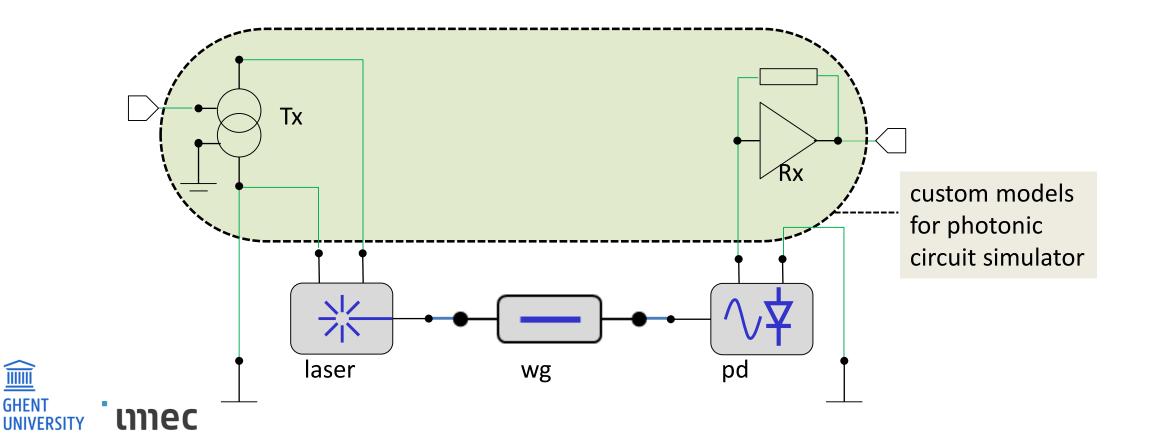

Simulate everything in a photonics simulator (Interconnect, Caphe, OptSim)

- Optimized models and formalisms for photonics

- Electronics models need to be mapped. No verified fab models

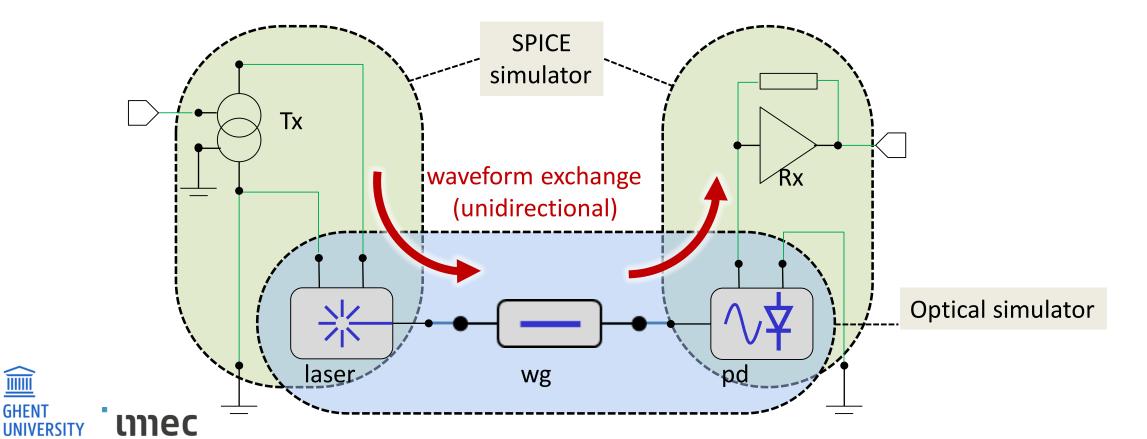

Co-simulate with waveform exchange

- Photonics and electronics in optimized model, executed sequentially

- Output of one simulation = input of next simulation

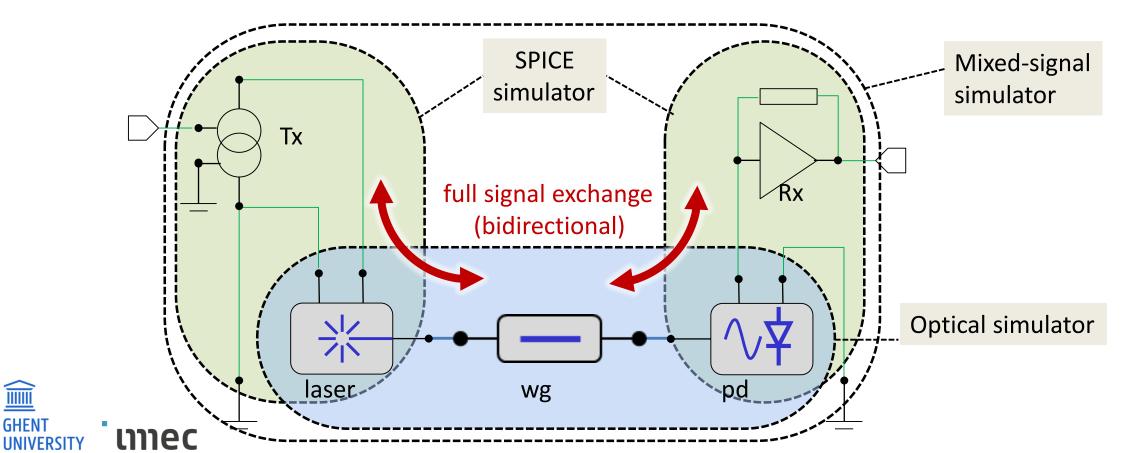

True cosimulation (photonics and electronics in lockstep)

- Both photonic and electronic simulators run in parallel ullet

- Photonic and electronic model exchange data at each step •

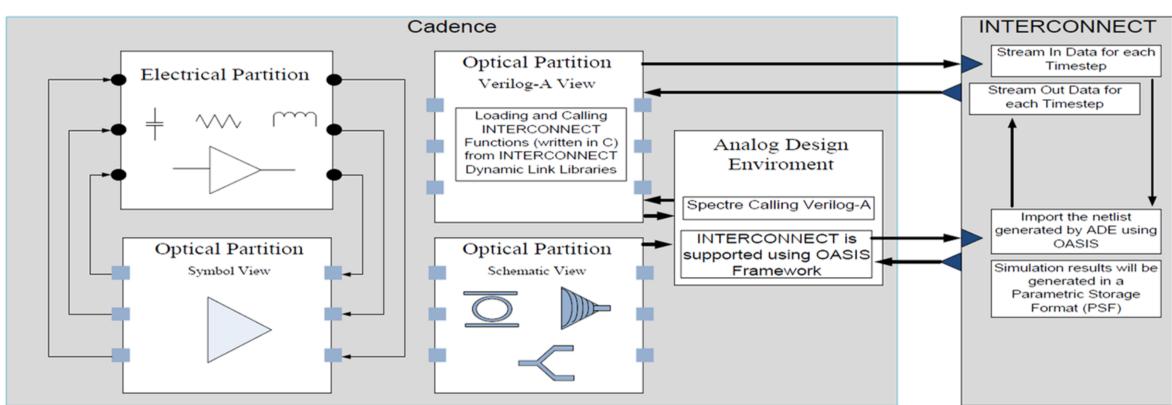

### **CO-SIMULATION**

Optical and electrical co-design in Virtuoso Schematic

Photonic simulation in Lumerical Interconnect

*Clumerical* **C ā d e n C e** A. Farsaei, APC 2016, JTu4A.1

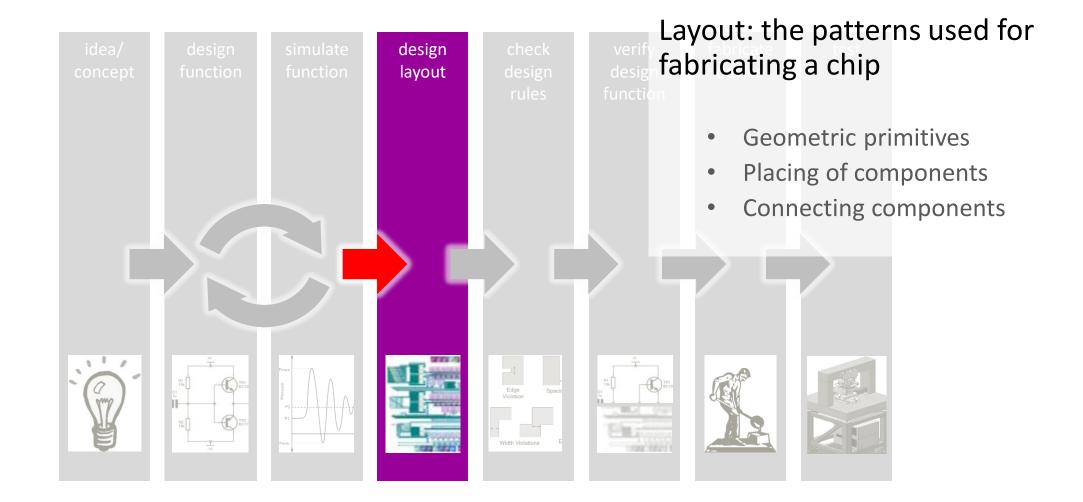

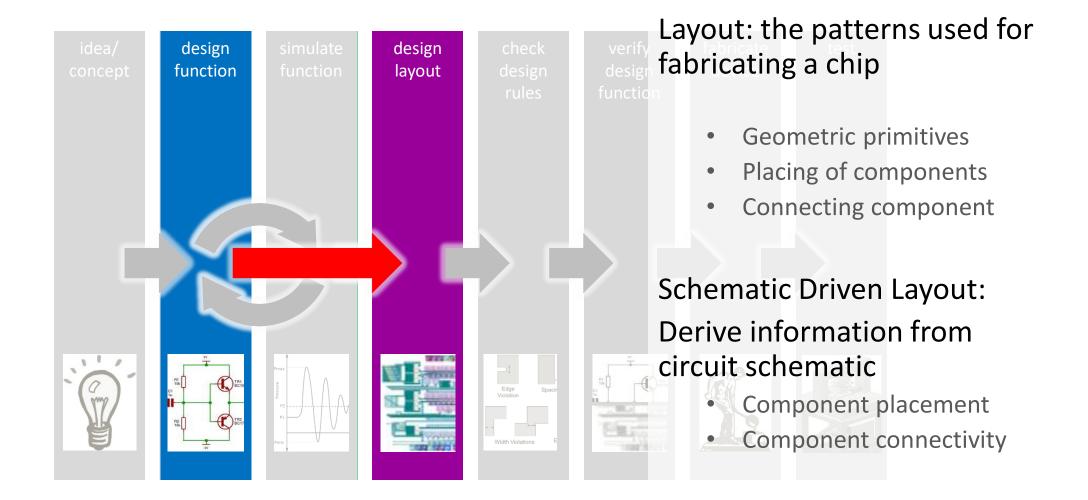

# FROM FUNCTION TO LAYOUT

**I** GHENT

UNIVERSITY

unec

design flow

82

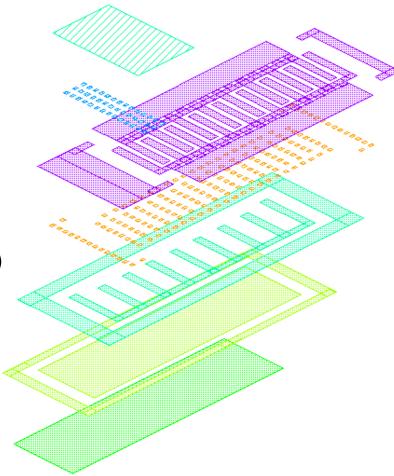

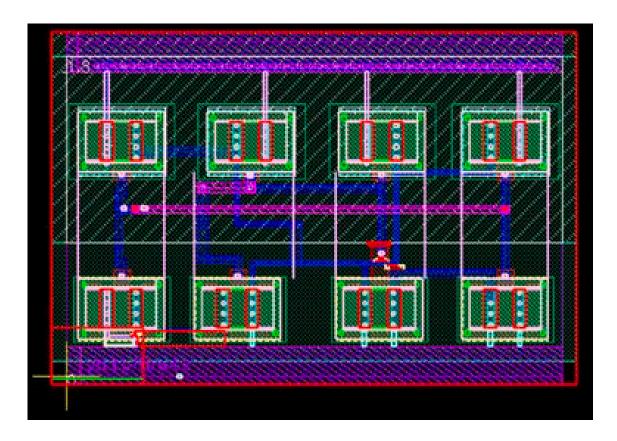

#### LAYOUT

#### Geometric patterns

- Originally drawn by hand

- Now drawn by computer

- or programmed using scripts

#### **Different layers**

- correspond to process steps: Mask layers

- or to logical operations (e.g. Boolean operations)

#### **Different purposes**

unec

GHENT

UNIVERSIT

• Intent of the drawn shape: process, exclusion, annotation, ...

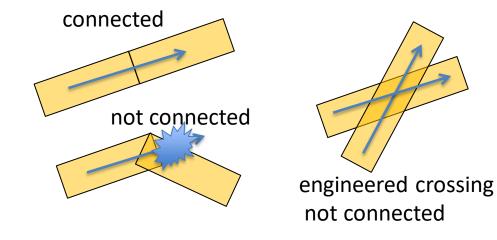

# LAYOUT: CIRCUITS

Organized in (reusable) Cells

- placement

- transformations

Hierarchy: Cells contain other cells

Routing

unec

**GHEN1**

UNIVERSITY

- Optical connectivity with waveguides

- Electrical connectivity with metal wiring

- Avoid crossings/shorts/disconnects

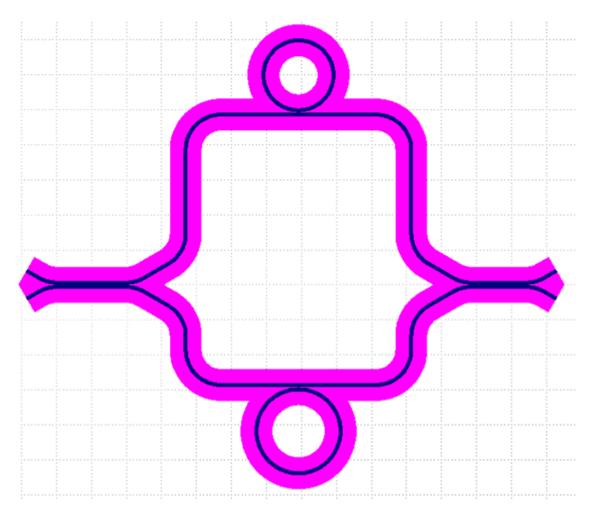

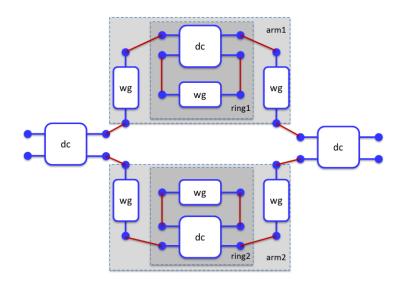

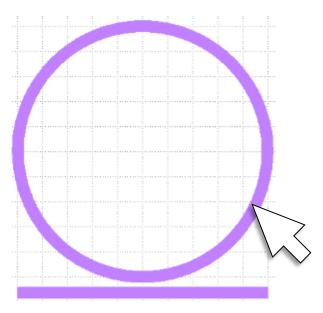

# PARAMETERIZED CELLS

(Or PCells)

#### Consists of

- Parameters

- that the user can supply

- Evaluators

- piece(s) of code that generate the content based on the parameters

Layout, model, symbol, netlist, ...

Languages:

**GHEN1**

UNIVERSITY

- Open: Tcl, Python, Ruby

- Proprietary: SKILL, Ample, SPT, ...

from ipkiss3 import all as i3

class RingResonator(i3.PCell):

class Layout(i3.LayoutView):

```

ring_radius = i3.PositiveNumberProperty(default=20.0)

wg_width = i3.PositiveNumberProperty(default=0.45)

coupler_gap = i3.PositiveNumberProperty(default=0.3)

```

def \_generate\_elements(self, elems):

r = self.ring\_radius

g = self.coupler\_gap

w = self.wg\_width

return elems

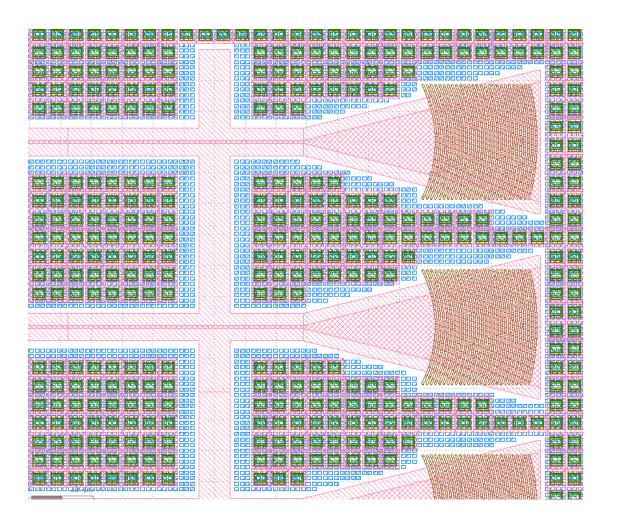

# SCHEMATIC DRIVEN LAYOUT (SDL)

design flow

time

# SCHEMATIC DRIVEN LAYOUT (SDL)

Derive the physical layout from the schematic

- Generate the Layout (P)Cells

- Place the Layout Cells

- Connect the layout cells together

### Not trivial to fully automate

- What is the optimal placement?

- Is the topology possible?

- Constraints for length matching?

- On which layer to route?

- Waveguide bends and crossings?

OFC 2018 – Short Course SC454

## PLACEMENT AND ROUTING

Photonic-specific constraints

- 'optical length' and phase control

- minimal bend radius

- waveguide spacing

- matching port direction

- single routing layer!

unec

**GHENT**

UNIVERSITY

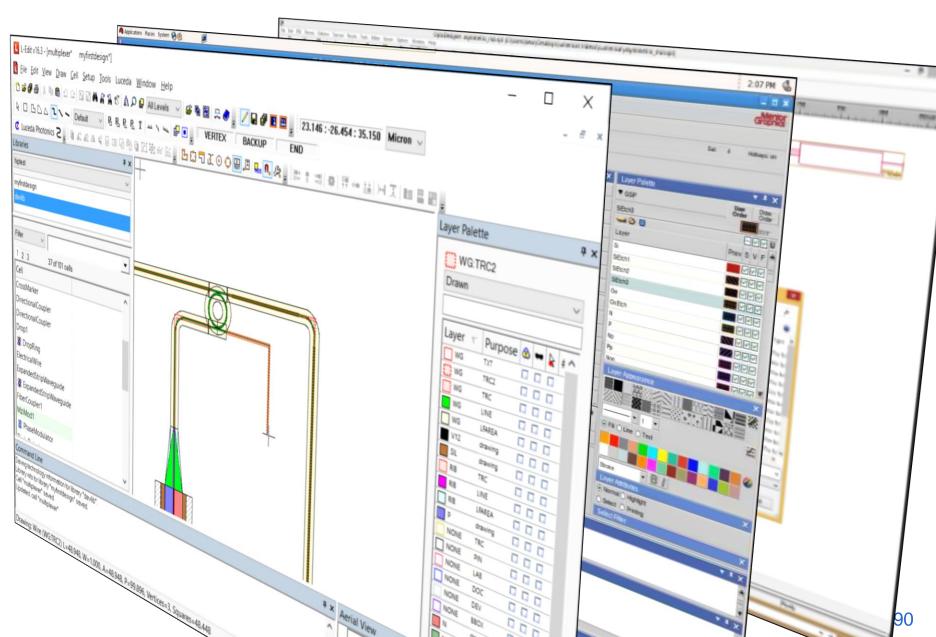

# PHOTONIC SDL TOOLS ARE EMERGING

Pure photonics or based on EDA tools

- define connections

- place components

- route waveguides

Luceda, Phoenix, Mentor Graphics,

unec

Cadence ...

GHENT

UNIVERSITY

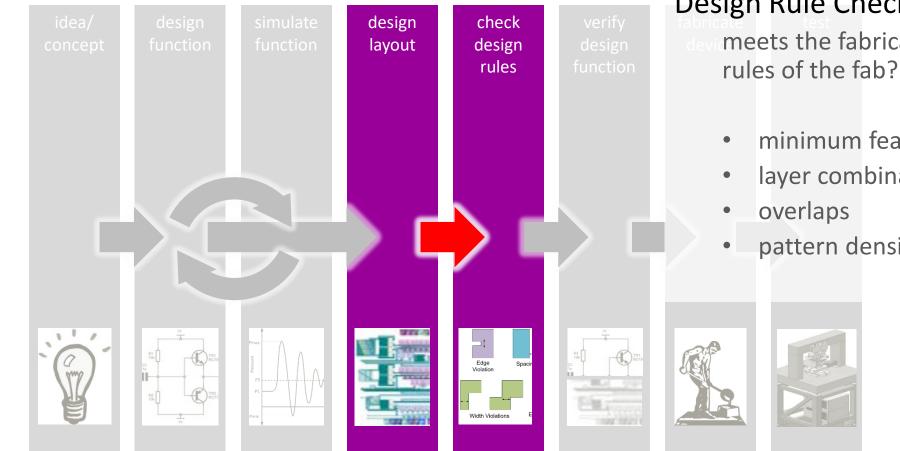

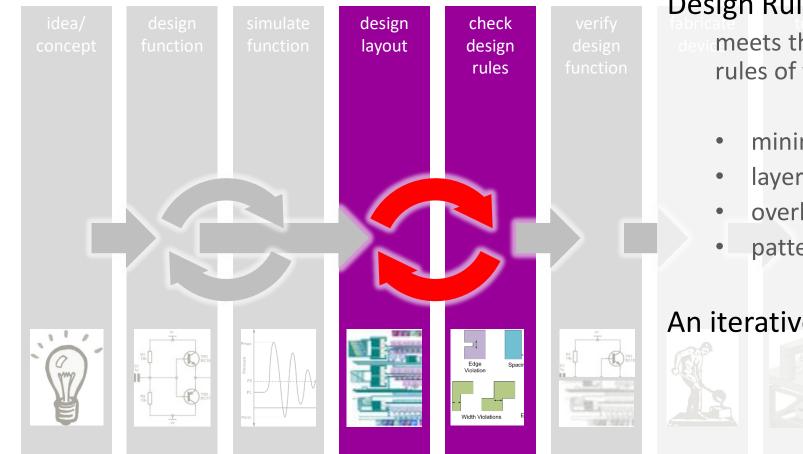

## IS THE LAYOUT VALID?

design flow

### **Design Rule Checking** meets the fabrication

- minimum features

- layer combinations

time

pattern density

**IIII** GHENT unec **UNIVERSITY**

91

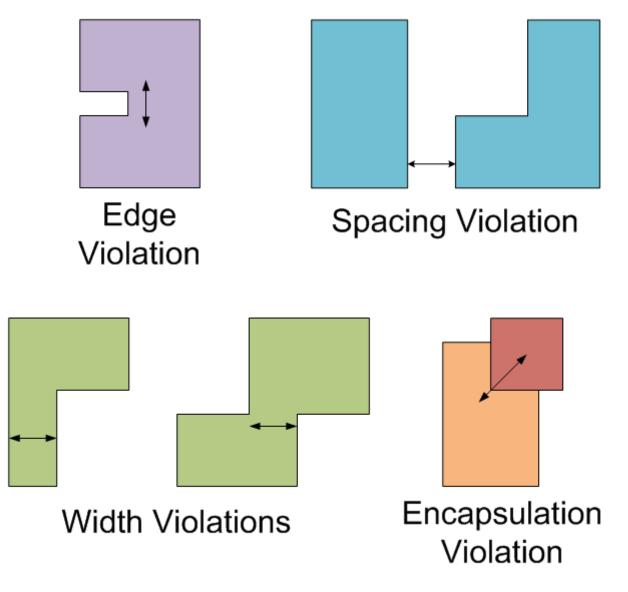

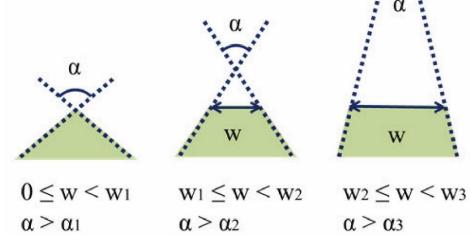

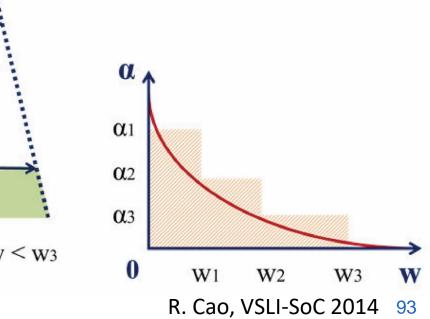

## DESIGN RULE VIOLATIONS: EXAMPLES

# PHOTONIC PROBLEMS WITH DRC?

DRC techniques were designed for electronics: 90-degree angles...

Silicon Photonics:

- All-angle waveguides discretized...

- Nanometer scale sensitivities

- Arbitrary geometries (e.g. slot waveguides, PhC)

What is bad?

What is intentional?

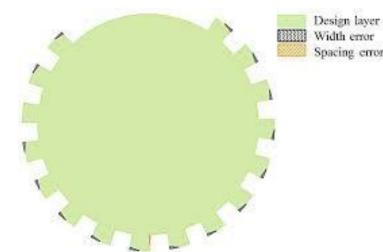

## PATTERN DENSITIES

Pattern density must be sufficiently uniform

- Etch rate control

- Avoid CMP dishing

Tiles are added

There must be sufficient room to add tiles

- Slab areas (AWG)

- Dense waveguide arrays

. . .

## IS THE LAYOUT VALID?

design flow

#### **Design Rule Checking** meets the fabrication rules of the fab?

- minimum features

- layer combinations

time

- overlaps

- pattern density

#### An iterative process

**IIII** GHENT unec **UNIVERSITY**

95

OFC 2018 – Short Course SC454

## **REAL-TIME DRC**

Layout is checked on DRC errors as it is being generated

Real-time feedback in editor

Much faster to a DRC-clean design

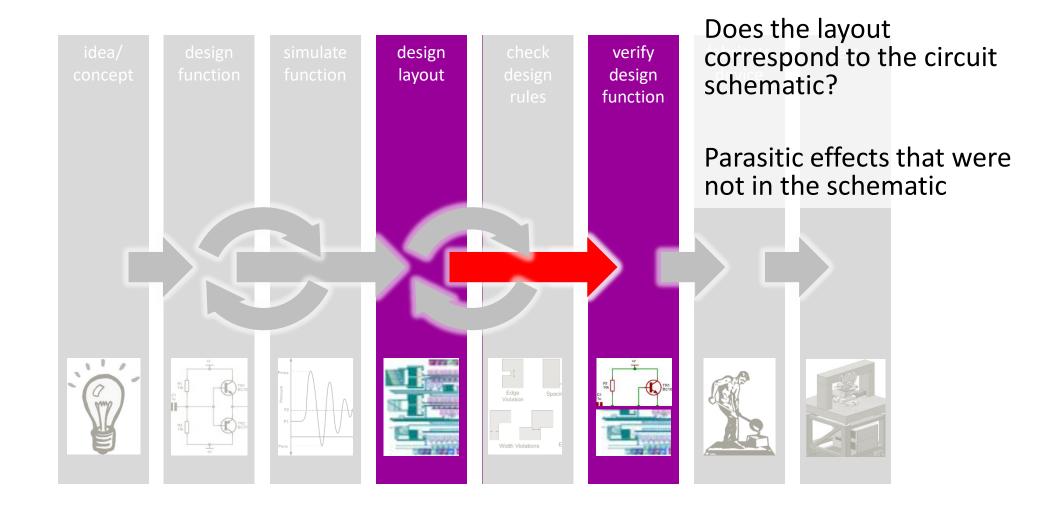

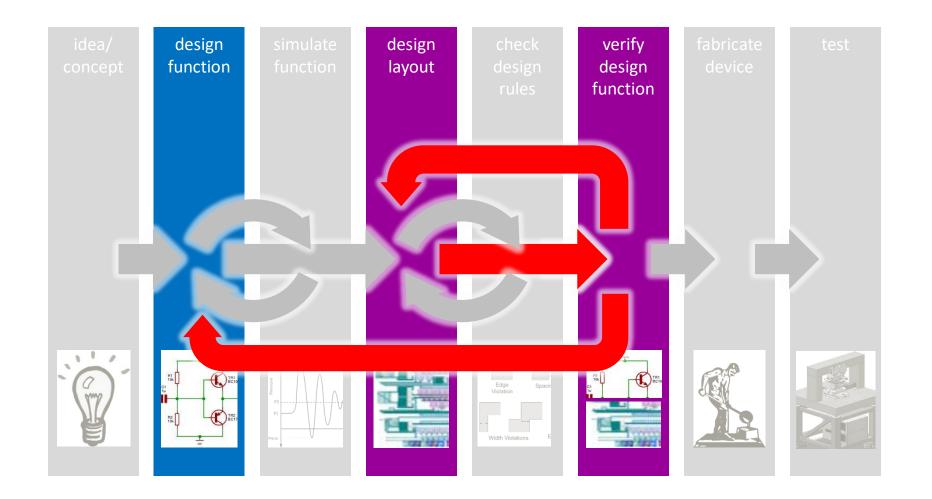

## **FUNCTIONAL VERIFICATION**

**IIII** GHENT

**UNIVERSITY**

unec

design flow

97

# FUNCTIONAL VERIFICATION: LAYOUT VERSUS SCHEMATIC

## **Check Connectivity**

Are the correct components placed?

Are they properly connected?

**GHEN**

UNIVERSI

mec

## **Check functionality**

Did we use the right parameters?

Does the layout perform the correct function?

e.g. does the waveguide have the correct width (i.e. optical length)

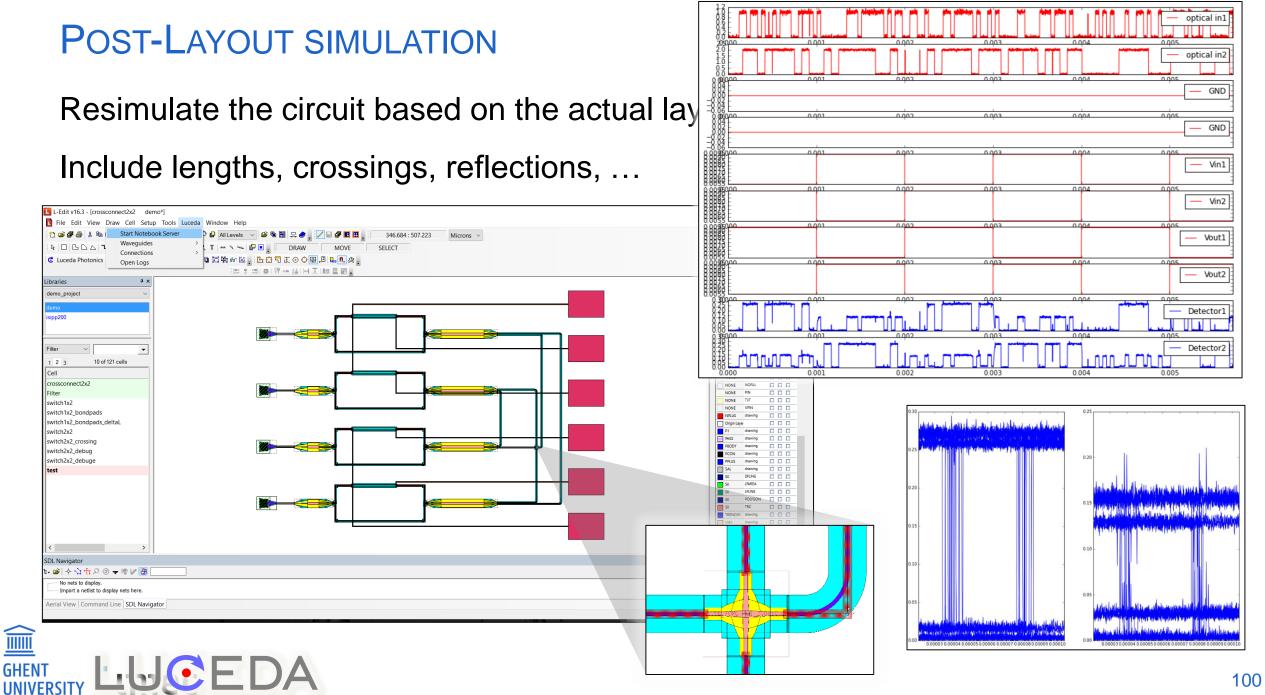

## **FUNCTIONAL VERIFICATION**

99

time

design flow

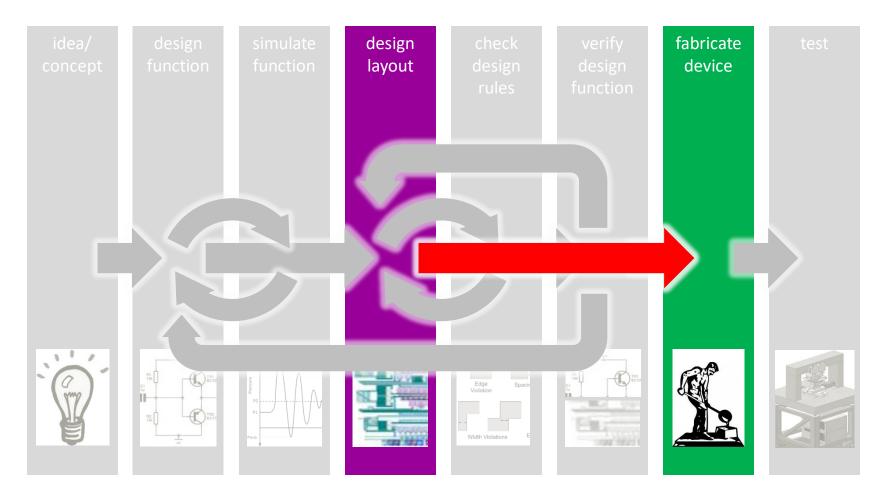

## FABRICATION

### *"no plan survives contact with the enemy"* H. von Moltke (misquoted)

time

design flow

## THE ACTUAL FABRICATION PROCESS

Layer depositions

Pattern definition (lithography)

Pattern transfer (etch)

Planarization

unec

. . .

**GHENT**

UNIVERSITY

Thermal treatment

Doping and implantation

example: IMEC silicon Photonics

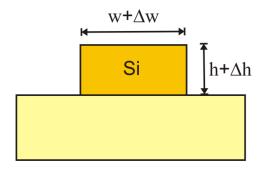

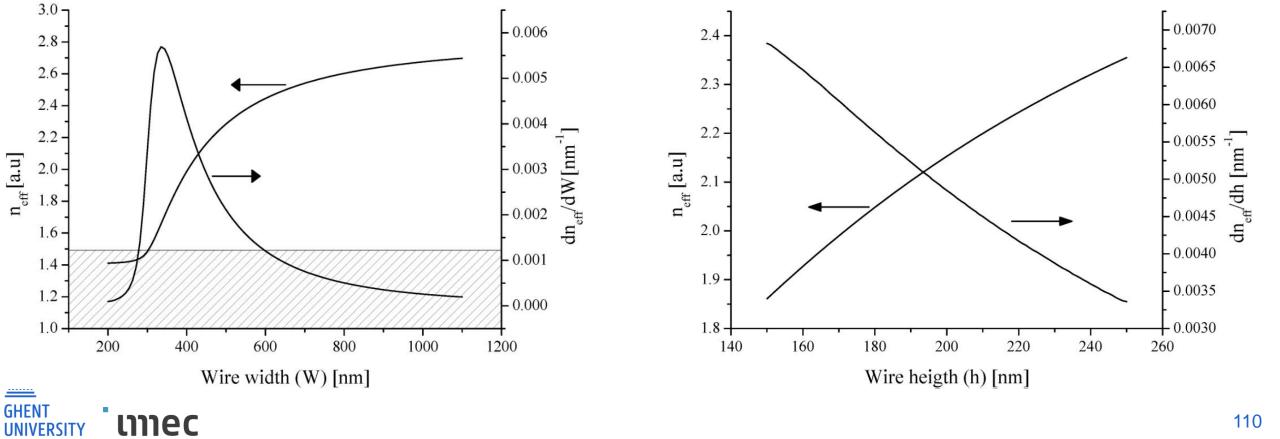

and each step with imperfections and variability

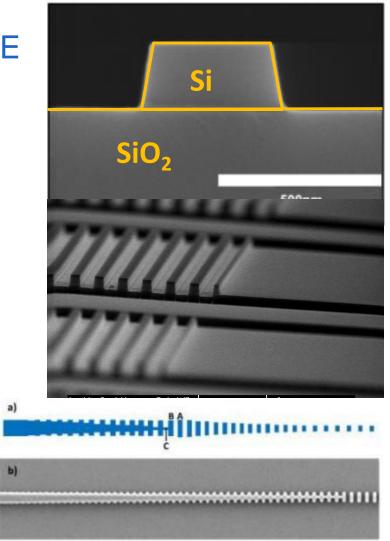

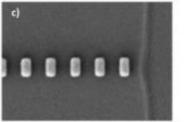

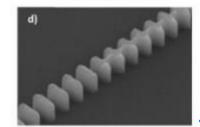

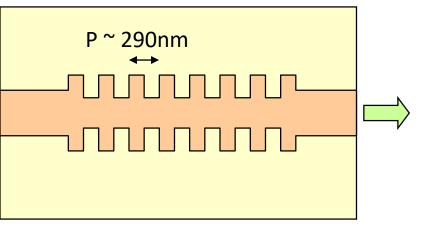

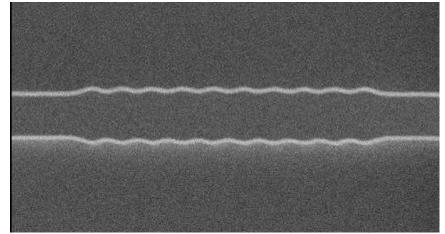

## LITHOGRAPHY: NOT PERFECT

## Spatial low-pass filter

- Minimum feature size

- Minimum pitch

- Pattern rounding

Example: Bragg grating

unec

**GHENT**

UNIVERSITY

103

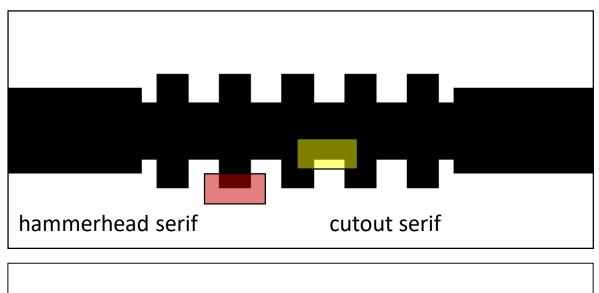

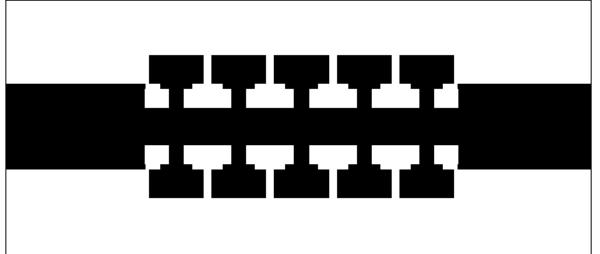

# **OPTICAL PROXIMITY CORRECTIONS (OPC)**

## Overcome rounding: add OPC

- serifs

- cutouts

Makes mask more complex (and costly)

unec

GHENT

UNIVERSITY

Not always possible without violating DR

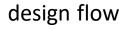

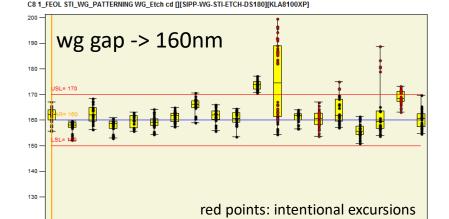

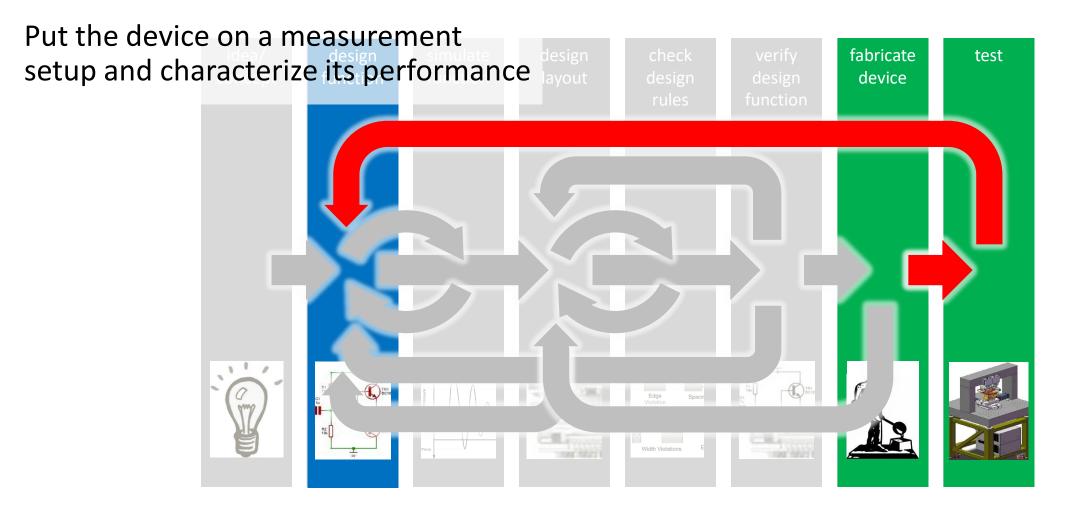

## FABRICATION: IN-LINE DATA

time

## **IN-LINE PROCESS DATA**

Collect data from wafers as they are being processed

- Line width

- Etch depth

- Layer thickness

Feed in design process

- FRONT-END: Predict behavioural change

- BACK-END: Adjust layout

C9 1\_FEOL STI\_WG\_PATTERNING WG\_Etch cd [][SIPP-WG-STI-ETCH-IL450][KLA8100XP]

### STATISTICS!

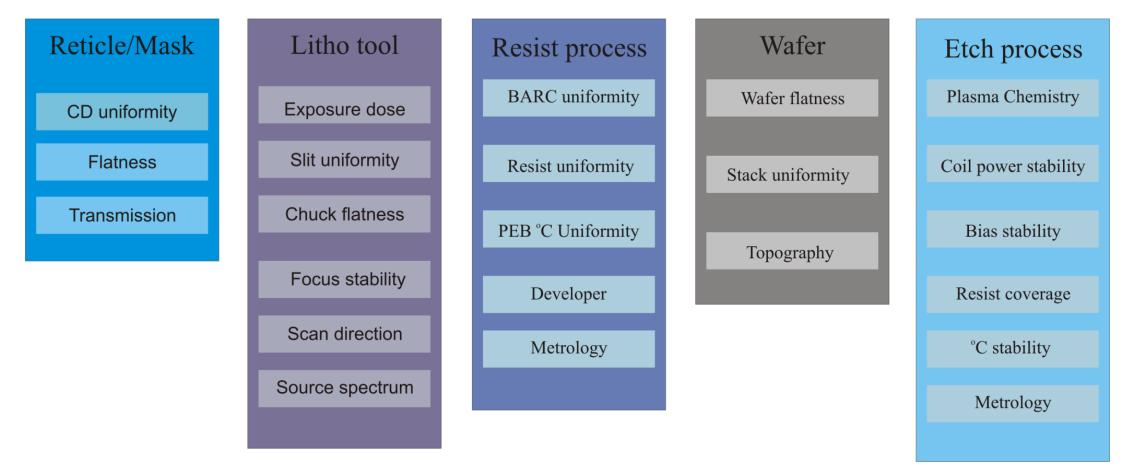

## THERE ARE MANY SOURCES OF NON-UNIFORMITY

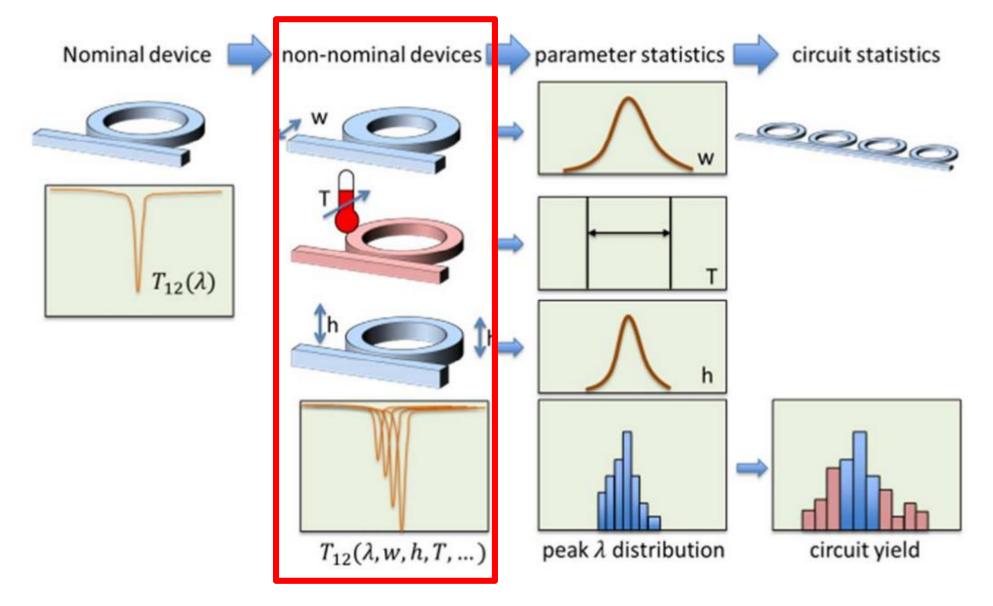

## VARIABILITY: PREDICTING CIRCUIT YIELD

**IIII** GHENT

UNIVERSITY

umec

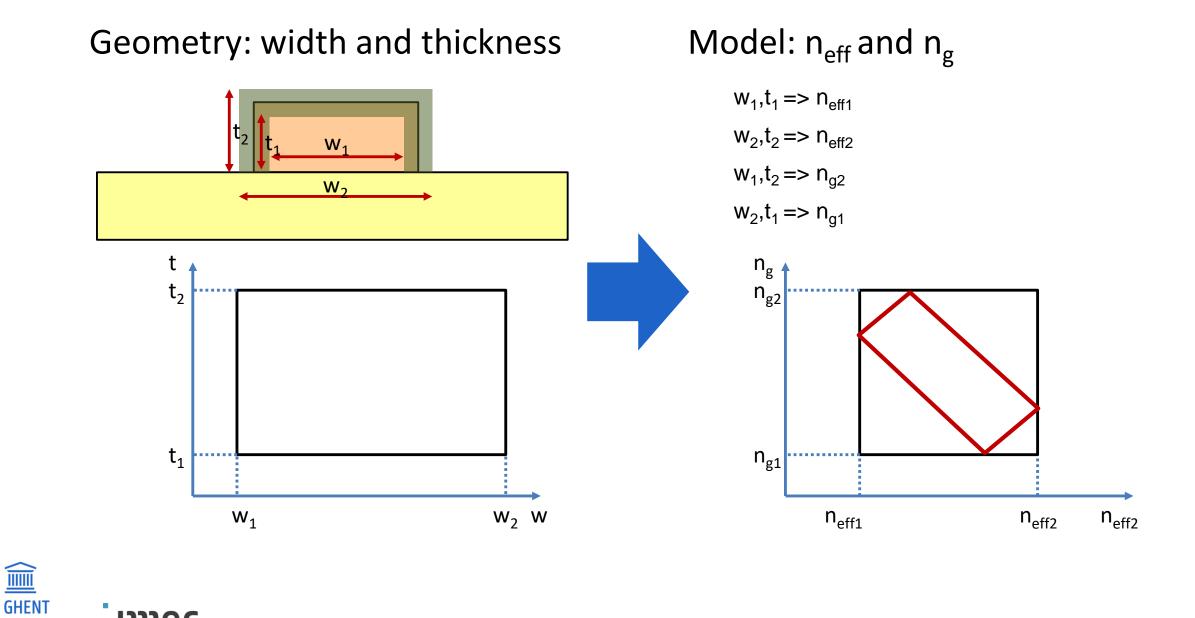

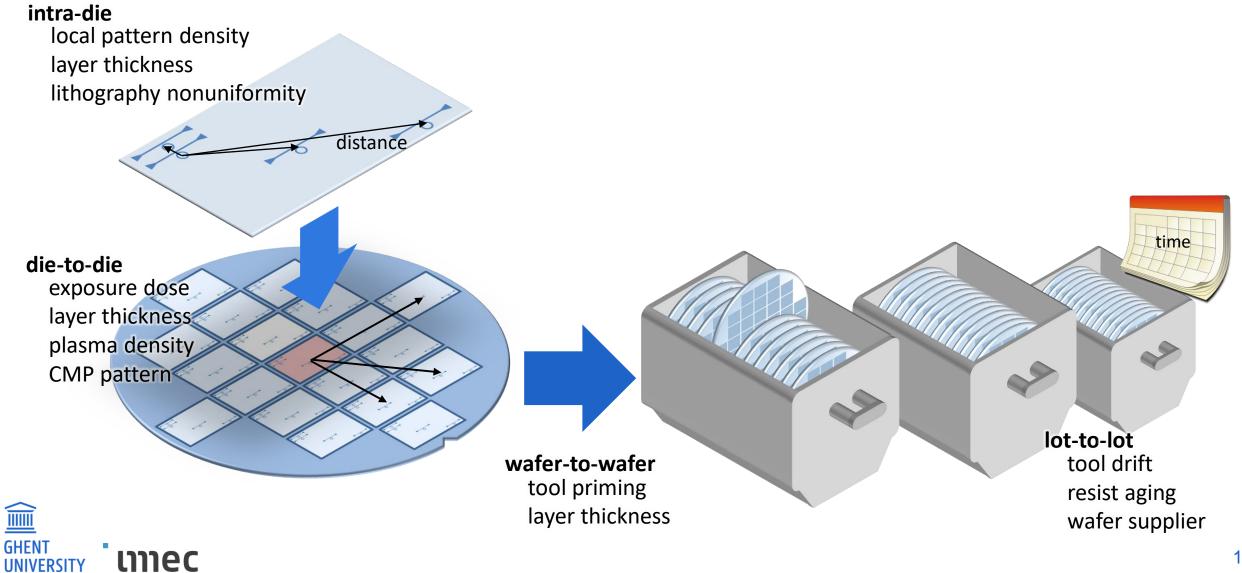

## **DESCRIBING VARIABILITY AT DIFFERENT LEVELS**

#### process conditions

• • •

**GHENT**

UNIVERSITY

exposure dose resist age plasma density slurry composition

unec

silicon

silicon dioxide

#### device geometry

...

w1

line width layer thickness sidewall angle doping profile

#### optical device properties

effective index group index coupling coefficients center wavelength

...

#### circuit properties

• • •

νπ

optical delay path imbalance tuning curve

<sup>L</sup>ring

#### system performance

...

insertion loss crosstalk noise figures power consumption

## LEVELS OF VARIABILITY: CAREFUL WITH MAPPING

unec

UNIVERSITY

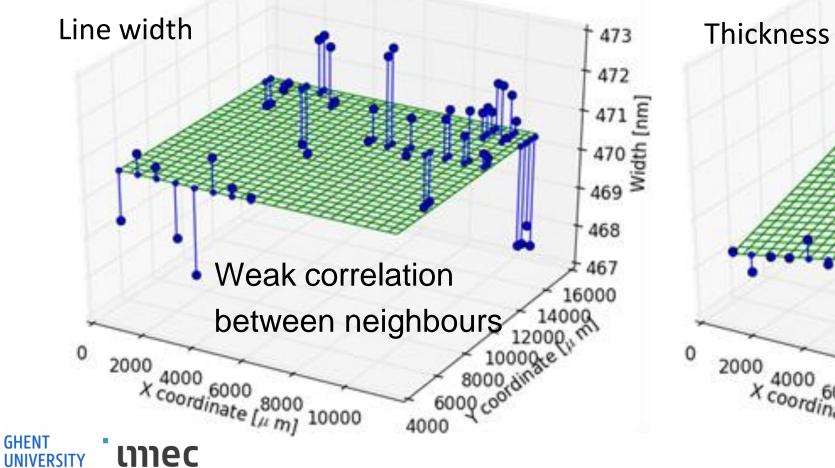

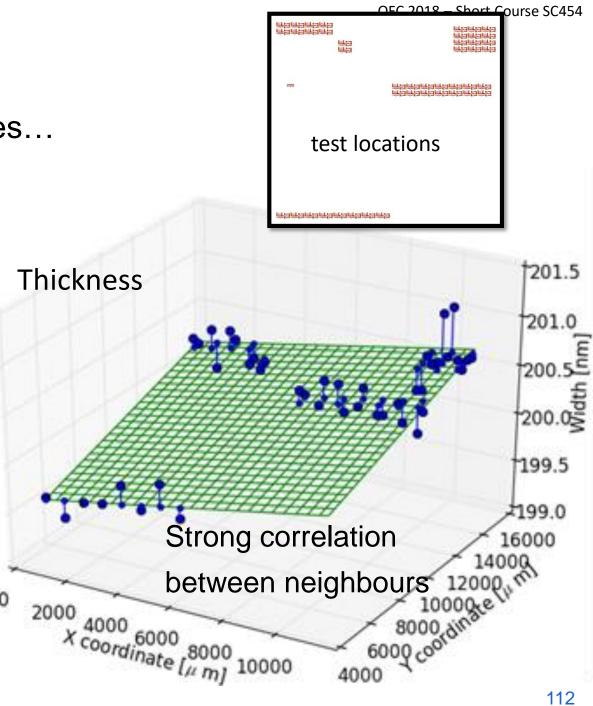

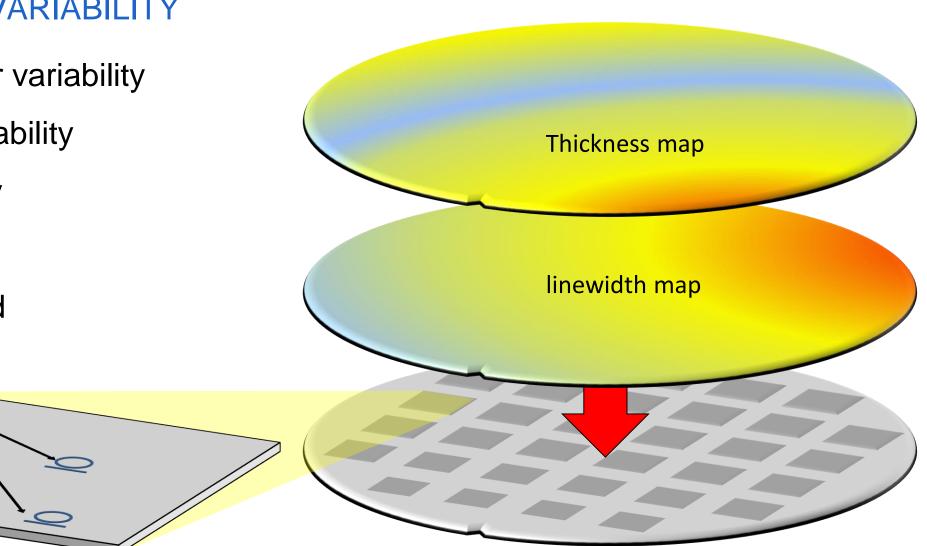

## **INTRA-DIE VARIABILITY**

Variability has causes with different properties...

Optical extraction of linewidth and thickness

## VARIABILITY EFFECTS WORK ON DIFFERENT SCALES

## VARIABILITY $\neq$ VARIABILITY

- Wafer to wafer variability

- Die to die variability

- Intra-die variability

- mask-related

- distance related

- stochastic

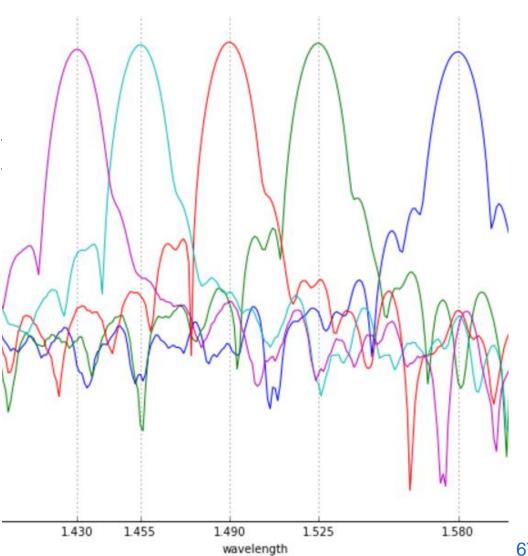

## **T**ESTING

design flow

115

time

OFC 2018 – Short Course SC454

## How to test?

Electrical, optical, or both?

Wafer-scale testing -> grating couplers

Testing after packaging?

Need statistics?

unec

depends

**IIII** GHENT

UNIVERSITY

## CHALLENGE: DEFINING GOOD TESTS

You need to think about tests during the design stage

- Which structures are representative?

- How can I isolate them?

- What parameters do I want to measure?

- How will I analyse/fit the data?

Parameters for your component models!

- What makes a good model?

GHENT

UNIVERSITY

mec

Example: waveguide model

- $n_{eff}(\lambda)$  -> polynomial?

- loss( $\lambda$ ) -> polynomial?

- nonlinearities?

How to measure  $n_{eff}$ ?

## OUR SIMPLE DESIGN FLOW

**IIII** GHENT

UNIVERSITY

ເກາຍc

design flow

time

## OUR SIMPLE DESIGN FLOW

**I** GHENT

UNIVERSITY

unec

design flow

time

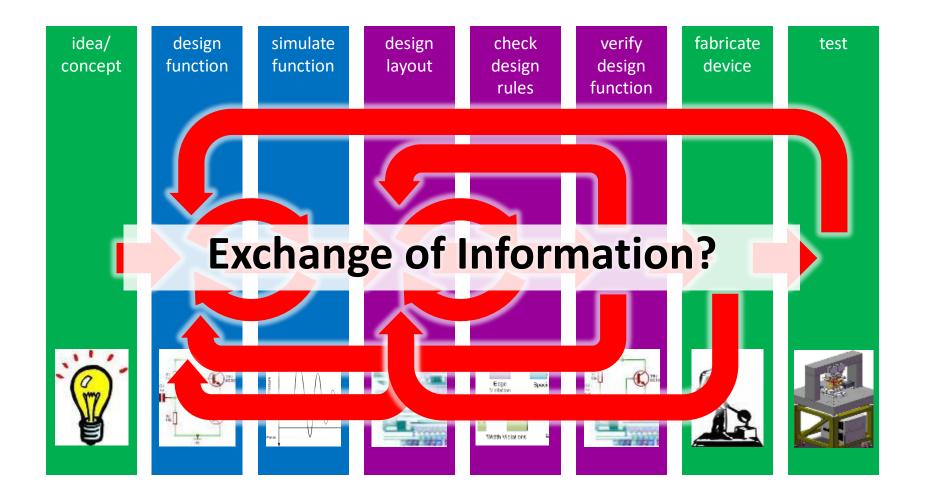

## **EXCHANGE OF INFORMATION**

#### Files

- Layout: GDSII and OASIS

- Netlist/Schematic: Spice, EDIF

- Models: Spice, VerilogA, C++, Python

- PCell code: Skill, Python , Tcl

- Data: Touchstone, XML

Databases

**GHENT**

UNIVERSIT

- proprietary

unec

- EDA standard: OpenAccess

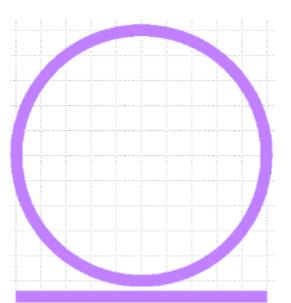

## DESIGNING IN CODE VERSUS GUI

#### **Designing in Code**

```

from ipkiss3 import all as i3

class RingResonator(i3.PCell):

class Layout(i3.LayoutView):

ring_radius = i3.PositiveNumberProperty(default=20.0)

wg_width = i3.PositiveNumberProperty(default=0.45)

coupler_gap = i3.PositiveNumberProperty(default=0.3)

def _generate_elements(self, elems):

r = self.ring_radius

g = self.coupler_gap

w = self.wg_width

elems += i3.CirclePath(layer=i3.Layer(2),

radius=r,

line_width=w)

elems += i3.Line(layer=Layer(2),

begin_coord=(-r, -r-w-g),

end_coord=(+r, -r-w-g),

line_width=w)

return elems

```

#### **Designing in GUI**

# DESIGNING IN CODE VERSUS GUI

#### **Designing in Code**

#### Pro:

- Easy to reuse

- Easy to upgrade design

- Easy to share and version

- Easy to parametrize

- Easy to document and make examples

- Everything is numerically correct

- Automate repetitive work

#### Con:

GHENT

UNIVERSITY

• Harder to learn

unec

No immediate visual feedback

#### **Designing in GUI**

#### Pro:

- Intuitive quick start

- Visual feedback

- WYSIWYG

- Quick point and click

#### Con:

- Difficult to make complex things

- No calculations

- A lot of manual work

- Easy make small (invisible) mistakes

# DESIGNING IN CODE VERSUS GUI

#### **Designing in Code**

- parameter sweeps

- calculated geometries

- circuit models

- automatic placement and routing

#### Designing in GUI

- schematic connectivity

- layout positioning (floorplanning)

- fixing the last DRC errors

- quick manual routing

OFC 2018 – Short Course SC454

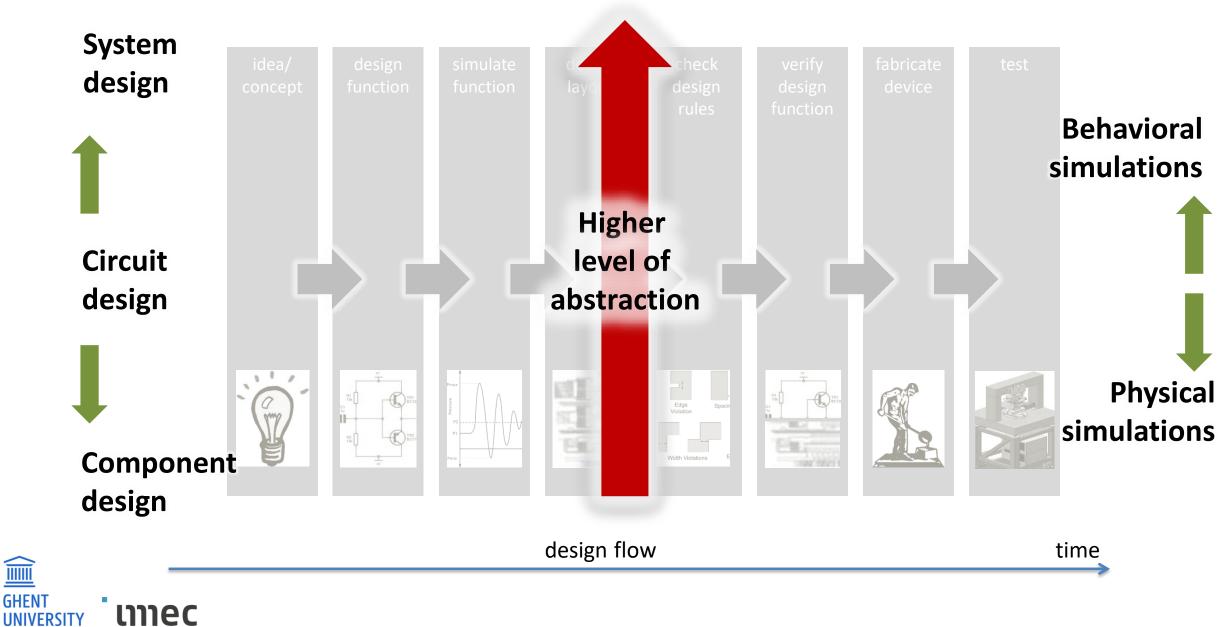

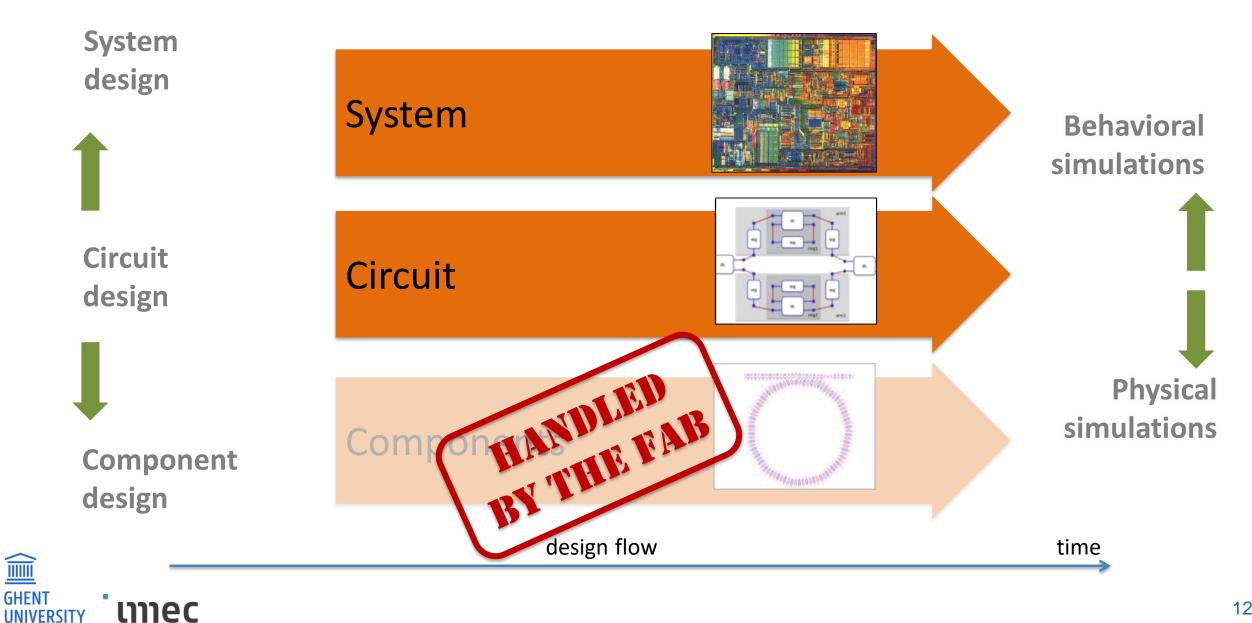

### **DESIGN ABSTRACTIONS**

**I** GHENT

#### **ABSTRACTIONS IN A CIRCUIT DESIGN FLOW**

## **ABSTRACTIONS IN A CIRCUIT DESIGN FLOW**

# PDK: INTERFACE FROM FAB TO DESIGNER

**GHENT**

#### SUMMARY

(Silicon) Photonics is growing towards a circuit platform

- Technology supports larger circuits

- A circuit-oriented design flow is emerging (similar to electronics)

- Fabs are building PDKs

Challenges

mec

**GHEN1**

- Schematic-driven Layout for photonics

- Variability: fabrication, performance, models

- Verification: DRC and LVS

- Design for manufacturability

- Photonic-electronic-software stacks

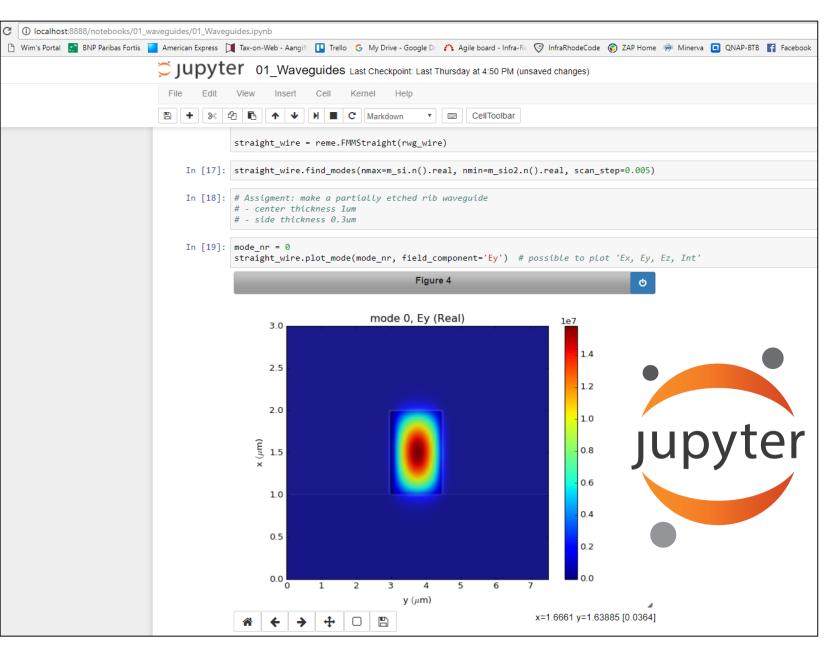

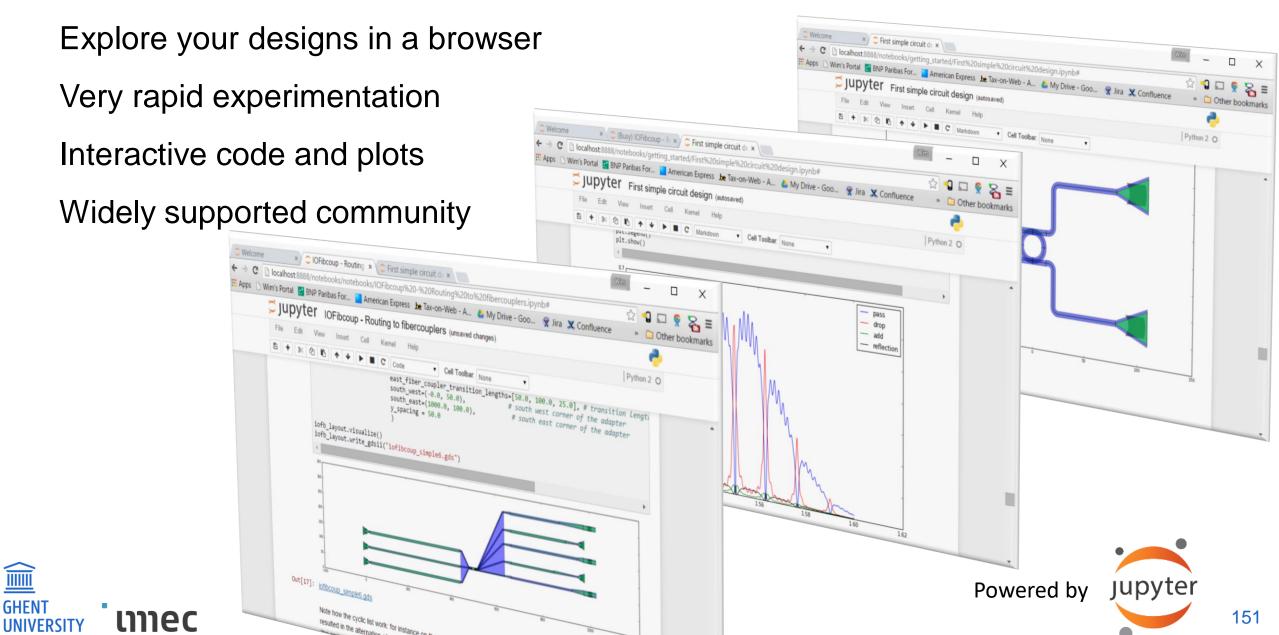

# PRACTICAL SETUP

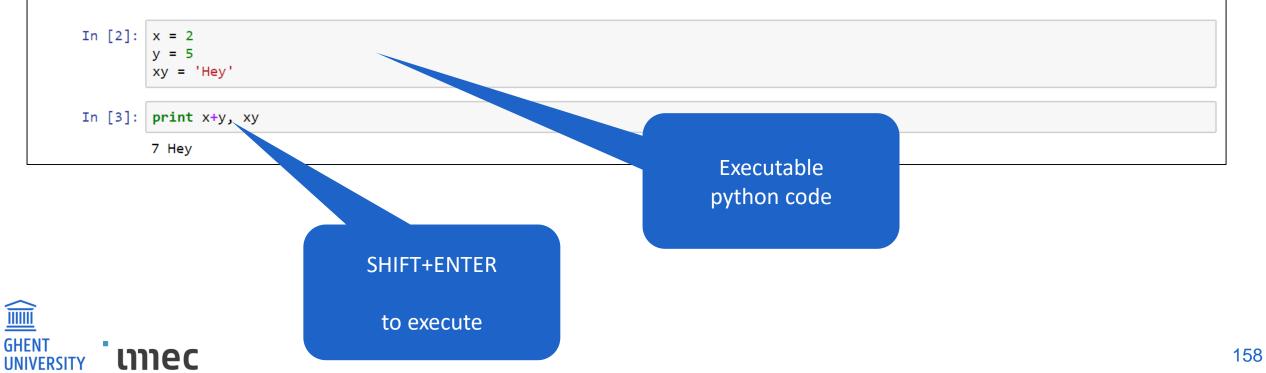

#### JUPYTER NOTEBOOKS

#### interactive notebook

- text, figures

- formulas

- python code

#### simulation and design

• built-in IPKISS

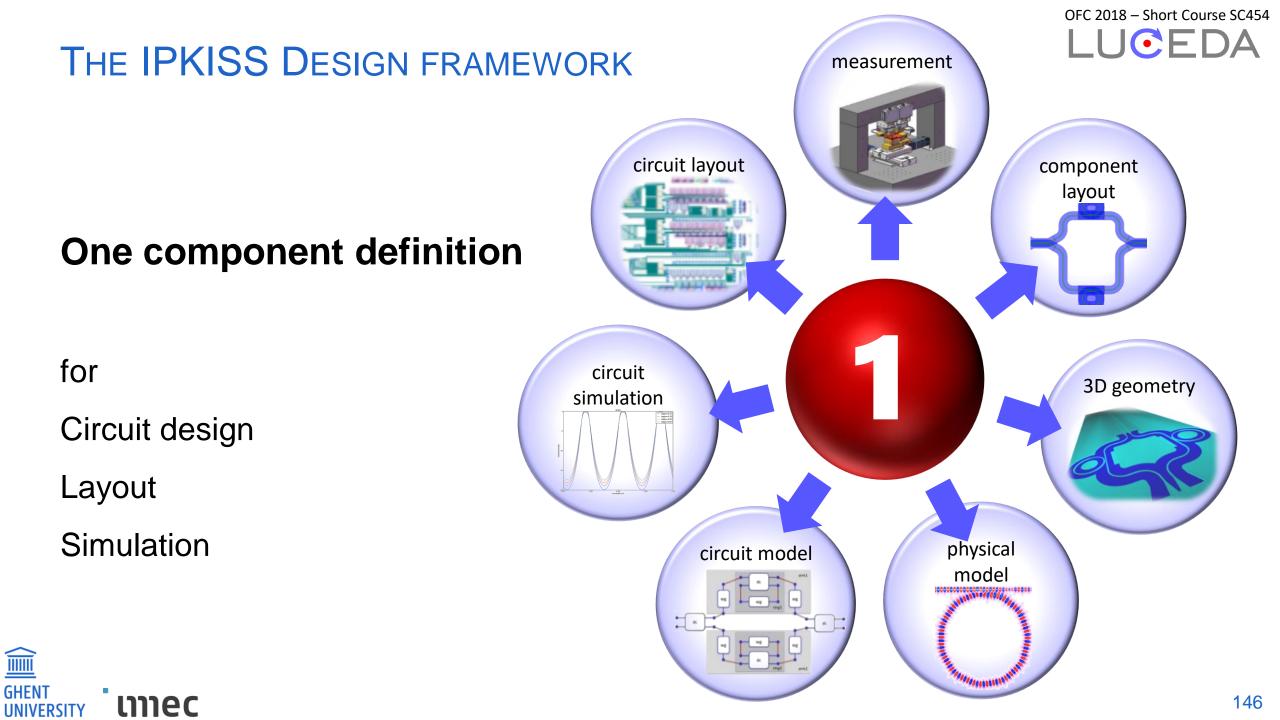

# THE IPKISS DESIGN FRAMEWORK

**Design framework for Photonic Integrated Circuits**

- Parametric design

- Focus on reuse and automation

History

- Developed at Ghent University imec in 2000-2014

- Spin-off into Luceda Photonics in 2014

- Currently hundreds of users worldwide

OFC 2018 – Short Course SC454

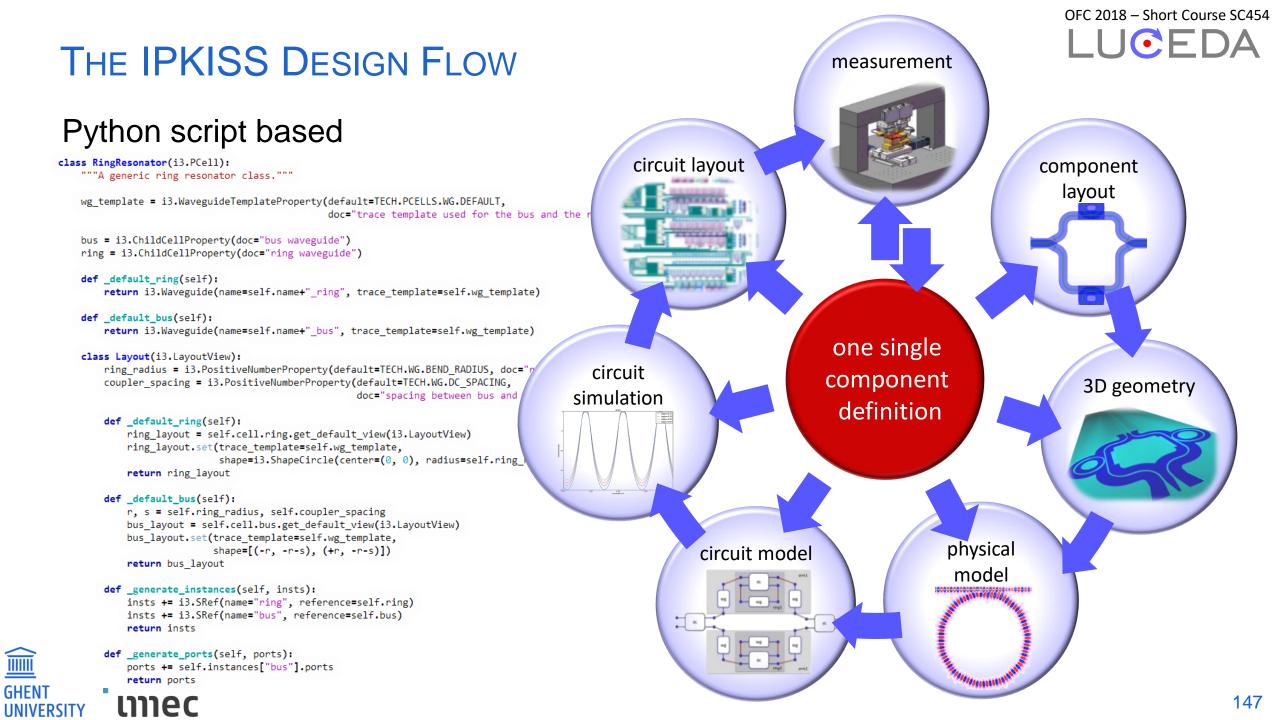

# THE IPKISS DESIGN FLOW

#### Python script based

#### class RingResonator(i3.PCell): """A generic ring resonator class."""

```

bus = i3.ChildCellProperty(doc="bus waveguide")

ring = i3.ChildCellProperty(doc="ring waveguide")

```

```

def _default_ring(self):

return i3.Waveguide(name=self.name+"_ring", trace_template=self.wg_template)

```

- def \_default\_bus(self):

return i3.Waveguide(name=self.name+"\_bus", trace\_template=self.wg\_template)

#### def \_default\_bus(self):

GHENT

UNIVERSITY

def \_generate\_instances(self, insts):

insts += i3.SRef(name="ring", reference=self.ring)

insts += i3.SRef(name="bus", reference=self.bus)

return insts

e python powered

- extremely flexible

- easy-to-read

- powerful engineering libraries

- industry standard

# THE PICAZZO LIBRARY

A large library of photonic components

- waveguides and routing

- crossings, splitters and couplers

- wavelength filters

- grating couplers and mode converters

- generic modulator blocks

- Parametric and technology aware

Validated on the IMEC technology platform

OFC 2018 – Short Course SC454

OFC 2018 – Short Course SC454

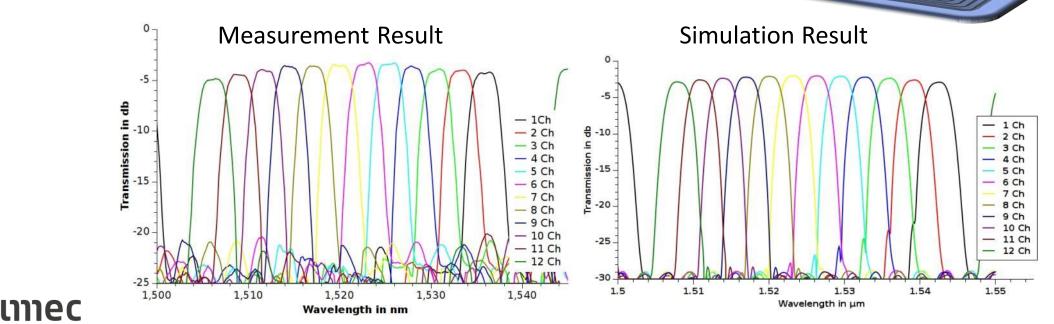

#### ADVANCED SPECTRAL FILTER DESIGN

Arrayed Waveguide Gratings

**Echelle Gratings**

**GHENT**

- Fully parametric

- Design from specifications

- Integrated layout and simulation

- Validated on fabricated devices

# **IPKISS NOTEBOOKS**

## **FIRST NOTEBOOKS**

Unfamiliar with Python?

/0\_1\_python\_getting\_started: basic Python tutorial /0\_2\_ numpy\_and\_plotting: Numpy and Matplotlib

Check if everything works and if you find your way around the notebook interface.

### PRACTICAL

- 1. Connect WIFI / Ethernet

- 2. Open web browser (Chrome, Firefox, Opera)

- 3. Connect to Jupyter server

(address will be provided on-site)

4. Log in with your personal ID/password

### NOTEBOOK: INTERACTIVE ENVIRONMENT

Text and explanations

#### Variables

A name that is used to denote something or a value is called a variable. In python, variables can be declared and values can be assigned to it as follows,

OFC 2018 – Short Course SC454

#### NAVIGATING

GHENT UNIVERSITY

| Files Running Clusters                   | Click here to go<br>back to start |                            |

|------------------------------------------|-----------------------------------|----------------------------|

| Select items to perform actions on them. |                                   | Upload New 🗸 📿             |

| • *                                      |                                   |                            |

| circuit_design                           |                                   |                            |

| circuit_simulation                       |                                   |                            |

| Component_design                         |                                   | Cuesta blan                |

| design_flows                             | Folders<br>with notebooks         | Create blan<br>notebook he |

| General dfm                              |                                   |                            |

| filter_design                            |                                   |                            |

| intro_ipkiss                             |                                   |                            |

| intro_python                             |                                   |                            |

| Iayout                                   |                                   |                            |

|                                          |                                   |                            |

### NAVIGATING

| 💭 Jupyter                                |                |              |

|------------------------------------------|----------------|--------------|

| Files Running Clusters                   |                |              |

| Select items to perform actions on them. |                | Upload New - |

| □ ▼                                      |                |              |

| ۵                                        |                |              |

| images_source                            | Notebook:      |              |

| □ □_tex                                  | click to start |              |

| images                                   |                |              |

| Ø0_Introduction.ipynb                    |                |              |

| 01_Basics_and_Built-in_Functions         | .ipynb         | Running      |

| 02_String                                |                |              |

| 03_Data Structures-                      |                |              |

| 04_String_and_Dicts.ipynb                | Running        |              |

| 05_Control_Flow.ipynb                    | Notebook       |              |

| Ø 06_Functions.ipynb                     |                |              |

| Ø7_Classes.ipynb                         |                |              |

| RSITY INNEC                              |                |              |

# PRESS H FOR 'HELP'

Useful menu and toolbar

Keyboard shortcuts are extremely powerful

| File       | dit View Insert Cell Kernel Help                                                                                                                                                                                                                                                                 |     |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>B</b> + | ※ ② ➡ ▲ ▲ ■ C Markdown ■ CellTool                                                                                                                                                                                                                                                                | bar |

|            | Keyboard shortcuts                                                                                                                                                                                                                                                                               |     |

|            | The Jupyter Notebook has two different keyboard input modes. <b>Edit mode</b> allows you to type code/text into a cell and is indicated by a green cell border. <b>Command mode</b> binds the keyboard to notebook level actions and is indicated by a grey cell border with a blue left margin. |     |

|            | Command Mode (press Esc to enable)                                                                                                                                                                                                                                                               |     |

|            | F: find and replace       Shift-J: extend selected cells below                                                                                                                                                                                                                                   |     |

|            | Ctrl-shift-P       : open the command palette       A: insert cell above                                                                                                                                                                                                                         |     |

|            | Enter : enter edit mode B : insert cell below                                                                                                                                                                                                                                                    |     |

|            | Shift-Enter     : run cell, select below     X : cut cell                                                                                                                                                                                                                                        |     |

|            | Ctrl-Enter     : run selected cells     C: copy cell                                                                                                                                                                                                                                             |     |

|            | Alt-Enter     : run cell, insert below     Shift-V                                                                                                                                                                                                                                               |     |

|            | Y: to code   V: paste cell below                                                                                                                                                                                                                                                                 |     |

|            | M: to markdown   Z: undo cell deletion                                                                                                                                                                                                                                                           |     |

|            | R: to raw   D, D: delete selected cell                                                                                                                                                                                                                                                           |     |

|            | 1: to heading 1 Shift-M: merge selected cells, or current                                                                                                                                                                                                                                        |     |

|            | 2: to heading 2cell with cell below if only one cell                                                                                                                                                                                                                                             |     |

|            | Image: selected                                                                                                                                                                                                                                                                                  |     |

|            | 4 : to heading 4 Ctrl-S : Save and Checkpoint                                                                                                                                                                                                                                                    |     |

|            | 5: to heading 5   S: Save and Checkpoint                                                                                                                                                                                                                                                         |     |

|            | Close                                                                                                                                                                                                                                                                                            |     |

**IIII** GHENT

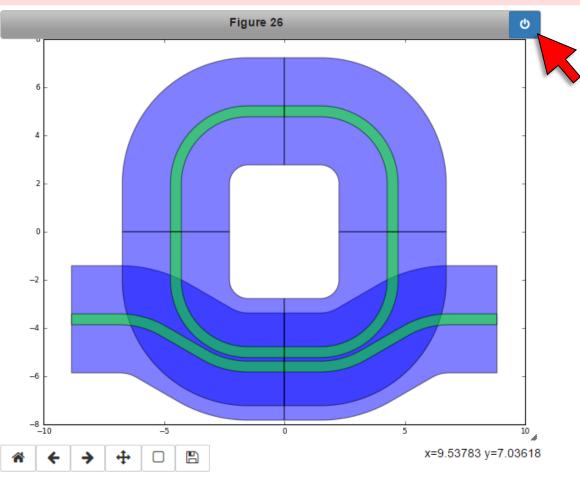

#### TAKE CARE OF MEMORY

Interactive plots consume resources.

Close them when ready.

C:\luceda\ipkiss\_311\python\envs\ipkiss3\lib\site-packages\matplotlib\pyplot.py:516: RuntimeWarning: More than 20 figures have been opened. Figures created through the pyplot interface (`matplotlib.pyplot.figure`) are retained until explicitly closed an d may consume too much memory. (To control this warning, see the rcParam `figure.max\_open\_warning`). max\_open\_warning, RuntimeWarning)

### Getting Started...

- connect to the internet

- open browser (Chrome, Firefox)

- connect to notebook server: https://wsjupyler.intec.ugent.be

- notebook login / password

Launch a notebook

Step 1: Copy the notebook

unec

GHENT

UNIVERSITY

📁 jupyter 02. IPKISS Layout elements Last Checkpoint: 6 hours ago (autosaved File Edit View Insert Help Cell Kernel С CellToolbar New Notebook Markdown 2002 Open... Make a Copy.. Rename... S Layout elements Save and Checkpoint Revert to Checkpoint ) ptebook we give an overview of predefined Layout elements in IPKISS. Th the user work a lot of common primitives are already provided. Print Preview Download as ► Trusted Notebook tup Close and Halt

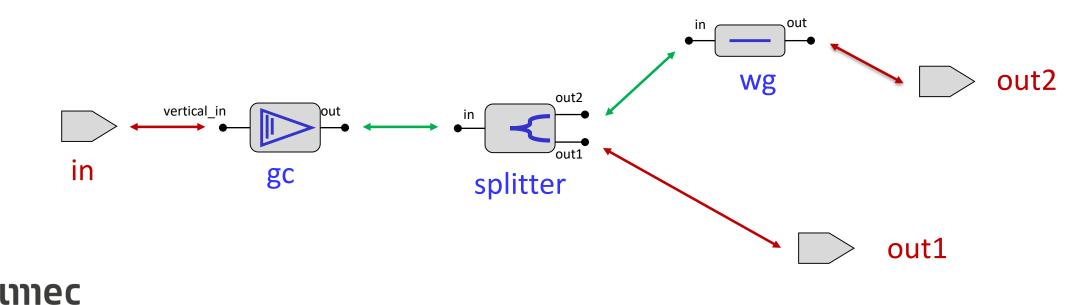

# BUILDING CIRCUITS IN A NOTEBOOK

#### Define schematics in python code

- List building blocks (or subcircuits)

- gc, splitter, wg

- List internal connections

- gc:out⇔splitter:in, splitter:out2⇔wg:in

- List external ports

GHENT

UNIVERSITY

• in ↔gc:vertical\_in, out1 ↔ splitter:out1, out2 ↔wg:out

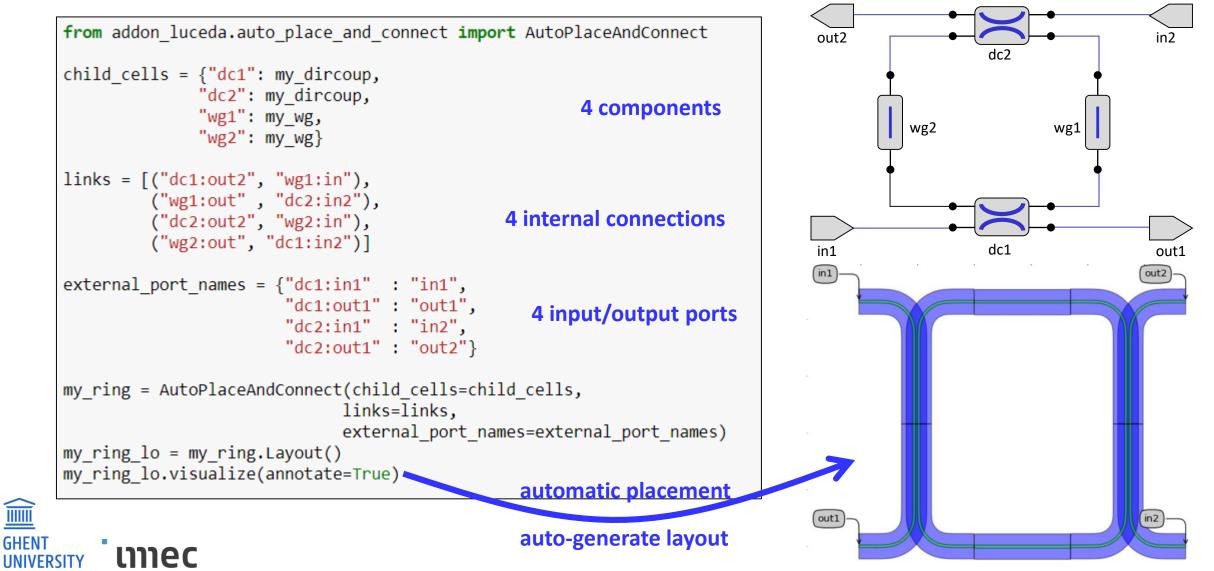

# BUILDING CIRCUITS: AUTOPLACEANDCONNECT

#### Circuits with direct connections: no waveguide generation

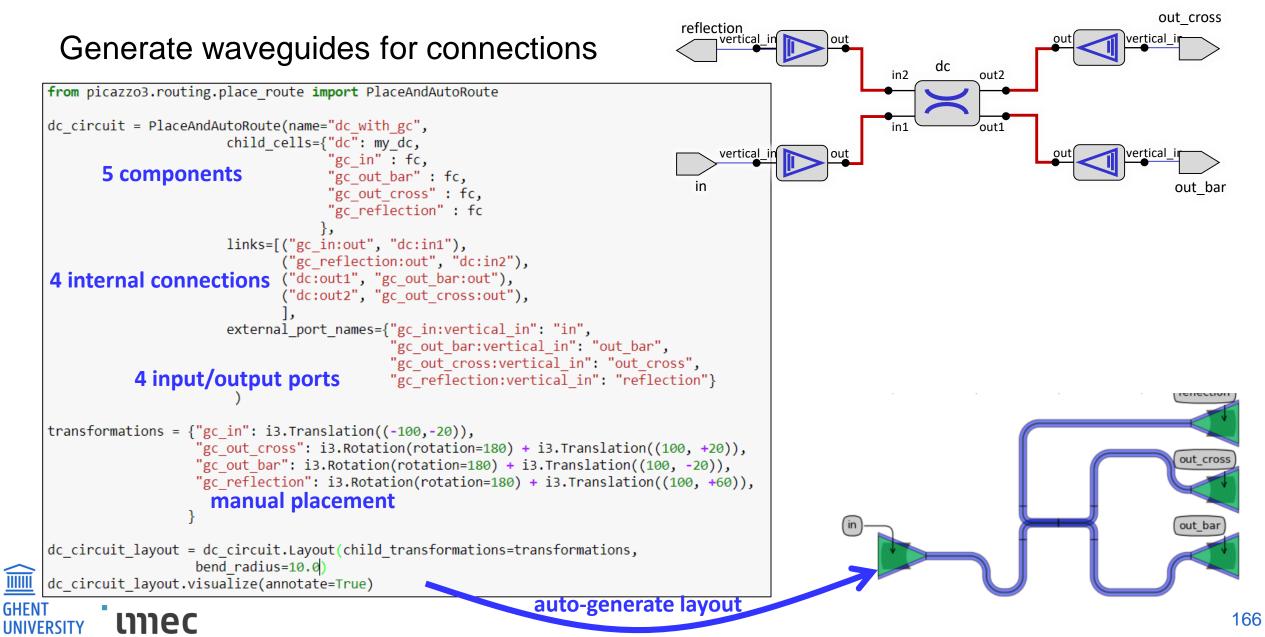

## BUILDING CIRCUITS: PLACEANDAUTOROUTE

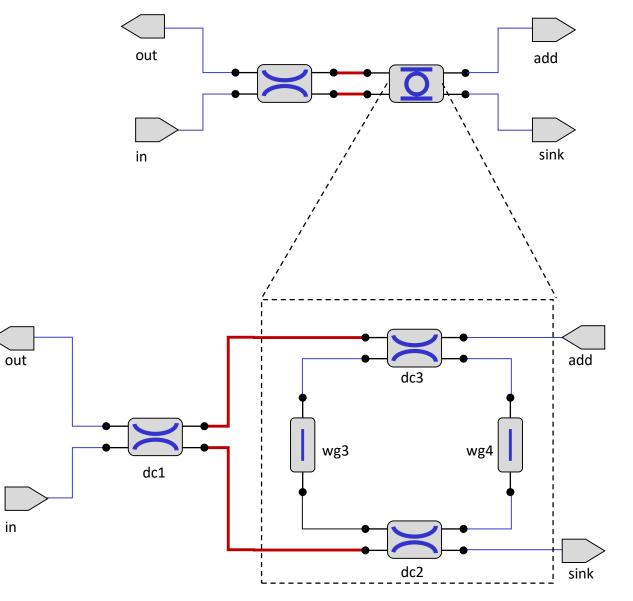

# USE HIERARCHY: YOU CAN USE A CIRCUIT AS A BUILDING BLOCK

Circuits can be nested

Break up circuits into reusable parts

## THE SMALL PRINT ON COPYRIGHT

The material on the server is copyrighted

- The IPKISS toolset

- The addon libraries

- The notebooks

Please do not download the material to your own PC. It will probably not work as the server has a specific set of pre-configured utilities.

If you interested in using IPKISS, contact info@lucedaphotonics.com If you are interested in using the course material, contact wim.bogaerts@ugent.be

You can continue to use the server until 30 June 2018.

#### **Further reading**

**Abstract** Silicon Photonics technology is rapidly maturing as a platform for larger-scale photonic circuits. As a result, the associated design methodologies are also evolving from componentoriented design to a more circuit-oriented design flow, that makes abstraction from the very detailed geometry and enables design on a larger scale. In this paper, we review the state of this emerging photonic circuit design flow and its synergies with electronic design automation (EDA). We cover the design flow from schematic capture, circuit simulation, layout and verification. We discuss the similarities and the differences between photonic and electronic design, and the challenges and opportunities that present themselves in the new photonic design landscape, such as variability analysis, photonic-electronic co-simulation and compact model definition.

# Silicon Photonics, Circuit Design: Methods, Tools and

#### Challenges

**GHENT**

UNIVERSITY

Wim Bogaerts<sup>1,2,\*</sup> and Lukas Chrostowski<sup>3</sup>

Lasers and Photonics Reviews

unec

OFC 2018 – Short Course SC454

#### **PHOTONICS RESEARCH GROUP**

#### Wim Bogaerts

- **Professor in Silicon Photonics**

- E wim.bogaerts@ugent.be

- T +32 9 264 3324

@PhotonicsUGent

www.photonics.intec.ugent.be

**N** FACULTY OF ENGINEERING